# **TPMC541**

# 32/16 Single-Ended or 16/8 Differential A/D Channels, 8/4 Voltage & Current Range D/A Channels and 8 LVTTL/TTL Digital I/O Channels

Version 1.0

### **User Manual**

Issue 1.0.1 May 2022

#### TPMC541-10R

32/16 Single-Ended/Differential A/D Channels, 8 Single-Ended D/A Channels and 8 LVTTL/TTL Digital I/O Channels

#### **TPMC541-20R**

16/8 Single-Ended/Differential A/D Channels, 4 Single-Ended D/A Channels and 8 LVTTL/TTL Digital I/O Channels

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. IP RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

©2020-2022 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description                                                                                   | Date            |

|-------|-----------------------------------------------------------------------------------------------|-----------------|

| 1.0.0 | Initial Issue                                                                                 | 29 January 2020 |

| 1.0.1 | Added chapter <i>Programming Hints</i> and sub-chapter <i>Global</i> DAC Status Register Read | May 2022        |

# **Table of Contents**

| 1 | PROD           | DUCT DESCRIPTION                                          | . 10 |

|---|----------------|-----------------------------------------------------------|------|

| 2 | TECH           | NICAL SPECIFICATION                                       | . 13 |

| 3 | HAND           | DLING AND OPERATION INSTRUCTIONS                          | . 15 |

|   |                | ESD Protection                                            |      |

|   |                | Power Dissipation                                         |      |

|   |                | Default Digital I/O Line State                            |      |

| 4 |                | RESS MAP(S)                                               |      |

| 4 |                | • •                                                       |      |

|   |                | PCI Configuration Space                                   |      |

|   |                | PCI Memory Space                                          |      |

|   | 4.2.1<br>4.2.2 |                                                           |      |

| _ |                | ·                                                         |      |

| 5 |                | STER DESCRIPTION                                          |      |

|   | 5.1 A          | A/D Global Registers                                      |      |

|   | 5.1.1          | Global ADC Control Register (0x000)                       |      |

|   | 5.1.2          | <b>5</b>                                                  |      |

|   |                | A/D Device Registers                                      |      |

|   | 5.2.1<br>5.2.2 |                                                           |      |

|   | 5.2.3          |                                                           |      |

|   | 5.2.4          |                                                           |      |

|   | 5.3 A          | A/D Sequencer Register                                    |      |

|   | 5.3.1          | A/D Sequencer Control Register (0x120)                    | 57   |

|   | 5.3.2          |                                                           |      |

|   | 5.3.3          |                                                           |      |

|   | 5.3.4<br>5.3.5 | <b>5</b> \ /                                              |      |

|   | 5.3.6          |                                                           |      |

|   | 5.3.7          |                                                           |      |

|   | 5.3.8          | A/D Sequencer DMA Buffer Next Address Register (0x148)    | 63   |

|   | 5.3.9          |                                                           |      |

|   |                | D/A Global Registers                                      |      |

|   | 5.4.1<br>5.4.2 |                                                           |      |

|   | -              | D/A Device Registers                                      |      |

|   | 5.5.1          | DAC Configuration Register(s) (0x168, 0x198)              |      |

|   | 5.5.2          | DAC Correction Register(s) (0x170 – 0x17C, 0x1A0 – 0x1AC) |      |

|   | 5.5.3          |                                                           |      |

|   | 5.5.4          |                                                           |      |

|   | 5.5.5          |                                                           |      |

|   |                | D/A Sequencer Register                                    |      |

|   | 5.6.1          | D/A Sequencer Control Register (0x2E8)                    |      |

|   | 5.6.2<br>5.6.3 |                                                           |      |

|   | 5.6.4          |                                                           |      |

|   | 5.6.5          | D/A Sequencer FIFO Level Register (0x2FC)                 | 80   |

|   | 5.6.6          |                                                           | 80   |

|   | 5.6.7                   | D/A Sequencer DMA Buffer Length Register (0x30C)              |     |

|---|-------------------------|---------------------------------------------------------------|-----|

|   | 5.6.8                   | D/A Sequencer DMA Buffer Next Address Register (0x310)        |     |

|   |                         | nversion Signal Registers                                     |     |

|   | 5.7.1                   | Conversion Clock 1 Generator Register (0x320)                 |     |

|   | 5.7.2                   | Conversion Clock 2 Generator Register (0x324)                 | 82  |

|   | 5.7.3                   | Frame Trigger Generator Register 1 (0x32C)                    |     |

|   | 5.7.4                   | Frame Trigger Generator Register 2 (0x330)                    |     |

|   | 5.7.5                   | Conversion Signal Generator Enable Register (0x33C)           |     |

|   | 5.7.6                   | Conversion Signal Generator Output Driver Register (0x340)    |     |

|   | 5.7.7                   | Conversion Signal Source Selection Register (0x344)           |     |

|   | 5.7.8<br><b>5.8 DIC</b> | Frame Timer Register (0x348)  > Registers                     |     |

|   |                         | DIO Input Register (0x354)                                    |     |

|   | 5.8.1                   |                                                               |     |

|   | 5.8.2<br>5.8.3          | DIO Input Filter Register (0x358) DIO Output Register (0x35C) |     |

|   | 5.8.4                   | DIO Output Register (0x350)                                   |     |

|   |                         | errupt Registers                                              |     |

|   | 5.9.1                   | Interrupt Enable Register                                     |     |

|   | 5.9.1.1                 | ·                                                             |     |

|   | 5.9.1.2                 | , ,                                                           |     |

|   | 5.9.1.3                 |                                                               |     |

|   | 5.9.1.4                 |                                                               |     |

|   | 5.9.2                   | Interrupt Status Register                                     |     |

|   | 5.9.2.1                 |                                                               |     |

|   | 5.9.2.2                 | · · · · · · · · · · · · · · · · · · ·                         |     |

|   | 5.9.2.3                 |                                                               | 99  |

|   | 5.10 Oth                | ner Registers                                                 |     |

|   | 5.10.1                  | Global Configuration Register (0x398)                         | 100 |

|   | 5.10.2                  | DIO Pull Reference Register (0x39C)                           |     |

|   | 5.10.3                  | P14 I/O Pull Reference Register (0x3A0)                       | 101 |

|   | 5.10.4                  | Correction Data EEPROM Control/Status Register (0x3A4)        | 102 |

|   | 5.10.5                  | Temperature Sensor Trigger Register (0x3A8)                   | 103 |

|   | 5.10.6                  | Temperature Sensor Data Register (0x3AC)                      |     |

|   | 5.10.7                  | Firmware Version Register (0x3FC)                             | 103 |

| 6 | DIGITA                  | L I/O                                                         | 104 |

|   | 6.1 Ge                  | neral Purpose Digital I/O (Front I/O)                         | 104 |

|   |                         | nversion Control Digital I/O (Rear I/O)                       |     |

| 7 |                         | G OUTPUTS                                                     |     |

| ' |                         |                                                               |     |

|   |                         | C Devices and D/A Channels                                    |     |

|   | 7.2 Ana                 | alog Output Ranges                                            |     |

|   | 7.2.1                   | Voltage Output Ranges                                         |     |

|   | 7.2.1.1                 |                                                               |     |

|   | 7.2.1.2                 | 1 6 1 6                                                       |     |

|   | 7.2.2                   | Current Output Ranges                                         |     |

|   |                         | A Data Coding                                                 |     |

|   |                         | A Data Correction                                             |     |

|   |                         | A Channel Range (Re-) Configuration                           |     |

|   | 7.6 DA                  | C Operating Mode                                              | 111 |

|   | 7.6.1                   | Manual Mode D/A Conversions                                   | 111 |

|   | 7.6.1.1                 |                                                               |     |

|   | 7.6.1.2                 |                                                               |     |

|   | 7.6.2                   | Sequencer Mode D/A Conversions                                | 112 |

| 8 | ANALO                   | G INPUTS                                                      | 113 |

| _ | <del></del>             |                                                               |     |

|     | 8.1          | ADC Devices and A/D Channels             | 113     |

|-----|--------------|------------------------------------------|---------|

|     | 8.2          | Analog Input Stage                       | 113     |

|     | 8.3          | Analog Input Sampling Scheme             | 114     |

|     | 8.4          | Analog Input Mode and Range              | 115     |

|     | 8.4.         | 1.1 Analog Input Mode                    | 115     |

|     | 8.4.         |                                          | 115     |

|     | 8.4.         |                                          | 116     |

|     | 8.5          | A/D Data Coding                          | 117     |

|     | 8.6          | A/D Data Correction                      | 117     |

|     | 8.7          | ADC Configuration                        | 118     |

|     | 8.8          | ADC Operating Mode                       | 118     |

|     | 8.8.         | 3.1 Manual Mode A/D Conversions          | 119     |

|     | 8.8.         | 3.2 Sequencer Mode A/D Conversions       | 119     |

| 9   | SEQ          | QUENCER OPERATION                        |         |

|     | 9.1          |                                          | 120     |

|     | 9.1.         | •                                        |         |

|     | 9.1.         |                                          |         |

|     | 9.1.         |                                          | 122     |

|     | 9.1.         | .4 Sequencer D/A Conversion              | 122     |

|     | • • •        |                                          | 122     |

|     | _            |                                          | 123     |

|     |              |                                          | 125     |

|     | 9.1.         | A/D Sequencer Operation                  |         |

|     |              |                                          |         |

|     | 9.2.<br>9.2. |                                          |         |

|     | _            |                                          | 127     |

|     |              |                                          |         |

|     |              |                                          |         |

|     | 9.2          |                                          | 131     |

|     | 9.2.         | · · · · · · · · · · · · · · · · · · ·    | 132     |

|     | 9.2.         |                                          | 133     |

|     | 9.3          | Combined D/A and A/D Sequencer Operation |         |

|     | 9.4          | Multi-Board Synchronization              |         |

|     | 9.5          |                                          | 136     |

|     | 9.6          |                                          | 137     |

|     | 9.6.         |                                          | 137     |

|     | 9.6.<br>9.6. |                                          | 138<br> |

|     |              |                                          | 138     |

|     |              |                                          |         |

|     | 9.6.         | 00                                       |         |

|     | 9.6.         |                                          | 139     |

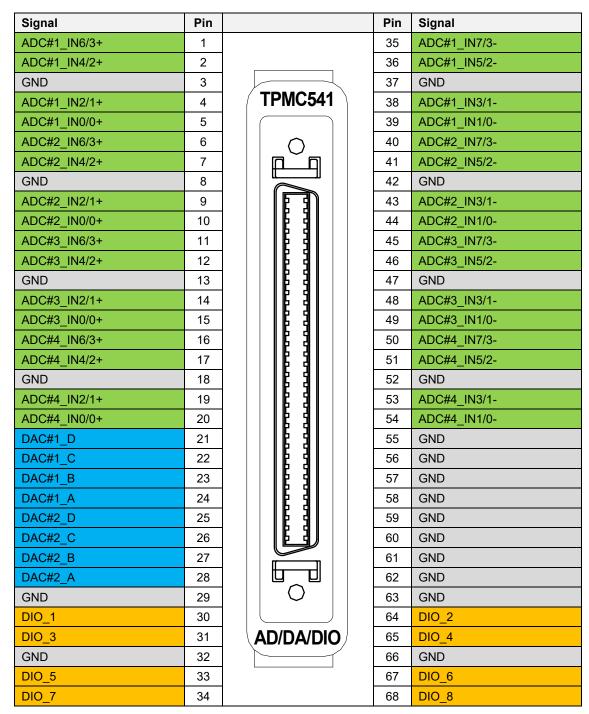

| 10  | I/O P        | PIN ASSIGNMENT                           | 140     |

| - • |              | Front I/O Connector                      |         |

|     |              | P14 Rear I/O Connector                   |         |

| 11  |              | OGRAMMING HINTS                          |         |

| 11  |              |                                          |         |

|     | 11.1         | Global DAC Status Register Read          |         |

# **List of Figures**

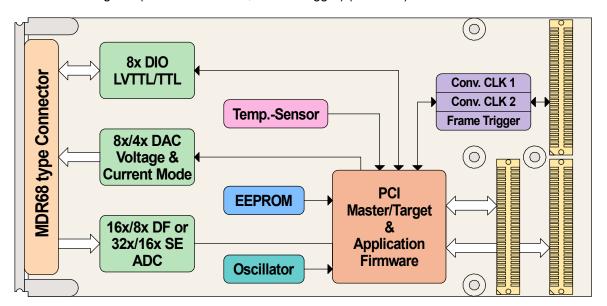

| FIGURE 1-1: TPMC541 BLOCK DIAGRAM                                    | 10  |

|----------------------------------------------------------------------|-----|

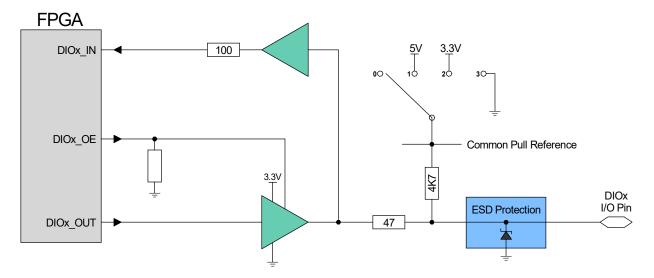

| FIGURE 6-1: DIGITAL I/O LINE CIRCUIT                                 | 104 |

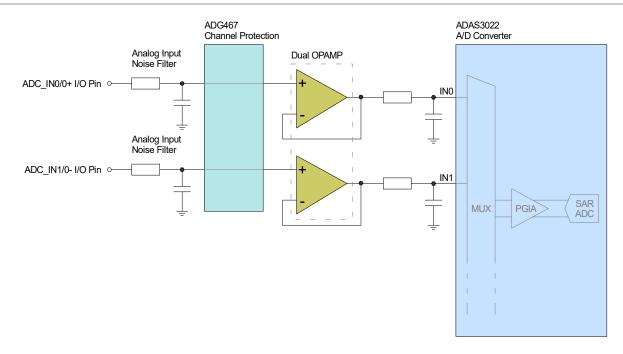

| FIGURE 8-1: ANALOG INPUT STAGE                                       | 114 |

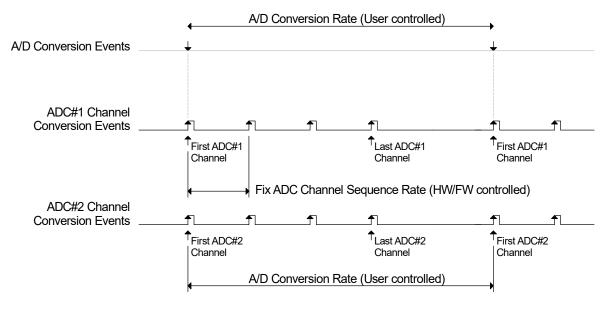

| FIGURE 8-2: ANALOG INPUT SAMPLING SCHEME                             | 114 |

| FIGURE 8-3: ANALOG INPUT SIGNAL RANGE SELECTION EXAMPLE              | 116 |

| FIGURE 9-1: D/A SEQUENCER UNIT                                       | 120 |

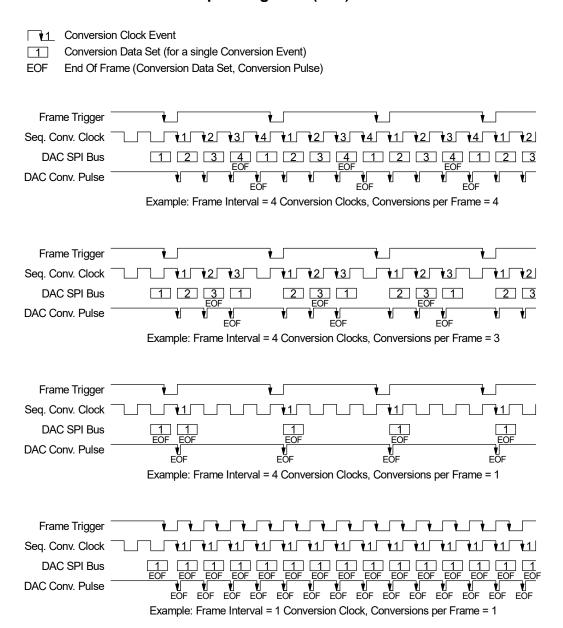

| FIGURE 9-2 : NORMAL MODE EXAMPLE DIAGRAM (D/A)                       | 123 |

| FIGURE 9-3: FRAME MODE EXAMPLE DIAGRAMS (D/A)                        | 125 |

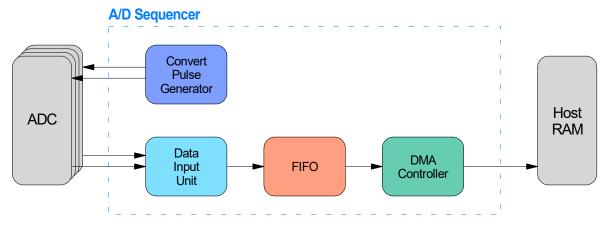

| FIGURE 9-4: A/D SEQUENCER UNIT                                       |     |

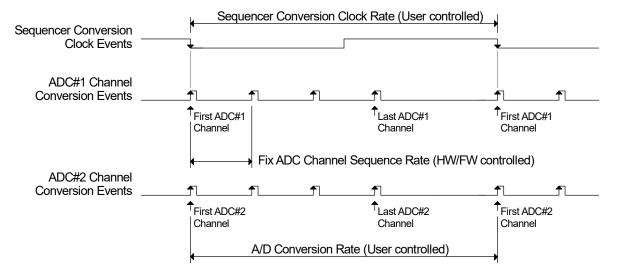

| FIGURE 9-5: A/D SEQUENCER SAMPLING SCHEME                            | 127 |

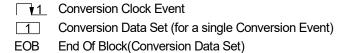

| FIGURE 9-6 : NORMAL MODE EXAMPLE DIAGRAM (A/D)                       | 129 |

| FIGURE 9-7 : FRAME MODE EXAMPLE DIAGRAMS (A/D)                       |     |

| FIGURE 9-8: D/A + A/D SEQUENCER OPERATION                            |     |

| FIGURE 9-9: COMBINED D/A & A/D SEQUENCER OPERATION IN FRAME MODE     |     |

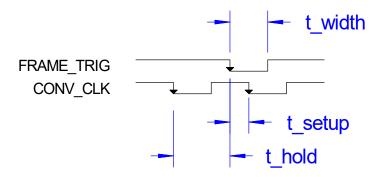

| FIGURE 9-10: FRAME TRIGGER TIMING REQUIREMENTS                       |     |

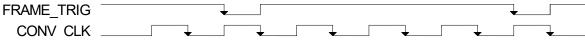

| FIGURE 9-11: SEQUENCER CONVERSION CONTROL SIGNALS OVERVIEW           | 137 |

| FIGURE 9-12: FRAME TRIGGER SIGNAL EXAMPLE (FRAME INTERVAL = 4)       | 138 |

|                                                                      |     |

| List of Tables                                                       |     |

| TABLE 2-1: TECHNICAL SPECIFICATION                                   | 14  |

| TABLE 4-1: PCI CONFIGURATION SPACE HEADER                            | 16  |

| TABLE 4-2: PCI MEMORY ADDRESS SPACES                                 | 17  |

| TABLE 4-3: REGISTER SPACE ADDRESS MAP                                | 21  |

| TABLE 4-4: CORRECTION DATA SPACE ADDRESS MAP                         | 47  |

| TABLE 5-1: REGISTER BIT ACCESS TYPES                                 | 48  |

| TABLE 5-2: GLOBAL ADC CONTROL REGISTER (0X000)                       |     |

| TABLE 5-3: GLOBAL ADC STATUS REGISTER (0X004)                        |     |

| TABLE 5-4: ADC X CONFIGURATION REGISTER (0X010, 0X054, 0X098, 0X0DC) | 52  |

| TABLE 5-5: ADC X CORRECTION REGISTER CHANNEL 0 (SE, DF)              | 53  |

| TABLE 5-6: ADC X CORRECTION REGISTER CHANNEL 1 (SE, DF)              | 53  |

| TABLE 5-7: ADC X CORRECTION REGISTER CHANNEL 2 (SE, DF)              | 53  |

| TABLE 5-8: ADC X CORRECTION REGISTER CHANNEL 3 (SE, DF)              | 53  |

| TABLE 5-9: ADC X CORRECTION REGISTER CHANNEL 4 (SE)                  |     |

| TABLE 5-10: ADC X CORRECTION REGISTER CHANNEL 5 (SE)                 |     |

| TABLE 5-11: ADC X CORRECTION REGISTER CHANNEL 6 (SE)                 |     |

| TABLE 5-12: ADC X CORRECTION REGISTER CHANNEL 7 (SE)                 |     |

| TABLE 5-13: ADC X DATA REGISTER CHANNEL 0/1 (SE, DF)                 |     |

| TABLE 5-14: ADC X DATA REGISTER CHANNEL 2/3 (SE, DF)                 |     |

| TABLE 5-15: ADC X DATA REGISTER CHANNEL 4/5 (SE)                     | 55  |

| TABLE 5-16: ADC X DATA REGISTER CHANNEL 6/7 (SE)                          | 55 |

|---------------------------------------------------------------------------|----|

| TABLE 5-17: ADC X MODE REGISTER (0X048, 0X08C, 0X0D0, 0X114)              | 56 |

| TABLE 5-18: A/D SEQUENCER CONTROL REGISTER (0X120)                        | 58 |

| TABLE 5-19: A/D SEQUENCER STATUS REGISTER (0X124)                         | 60 |

| TABLE 5-20: A/D SEQUENCER NUMBER OF CONVERSIONS REGISTER (0X12C)          | 61 |

| TABLE 5-21: A/D SEQUENCER CONVERSION COUNT REGISTER (0X130)               | 62 |

| TABLE 5-22: A/D SEQUENCER FIFO LEVEL REGISTER (0X134)                     | 62 |

| TABLE 5-23: A/D SEQUENCER DMA BUFFER BASE ADDRESS REGISTER (0X140)        | 63 |

| TABLE 5-24: A/D SEQUENCER DMA BUFFER LENGTH REGISTER (0X144)              | 63 |

| TABLE 5-25: A/D SEQUENCER DMA BUFFER NEXT ADDRESS REGISTER (0X148)        | 63 |

| TABLE 5-26: A/D SEQUENCER DMA BUFFER STATUS BASE ADDRESS REGISTER (0X14C) | 64 |

| TABLE 5-27: A/D SEQUENCER DMA BUFFER STATUS WORD (HOST RAM)               | 64 |

| TABLE 5-28: GLOBAL DAC CONTROL REGISTER (0X158)                           | 65 |

| TABLE 5-29: GLOBAL DAC STATUS REGISTER (0X15C)                            | 66 |

| TABLE 5-30: DAC X CONFIGURATION REGISTER (0X168, 0X198)                   | 68 |

| TABLE 5-31: DAC X CORRECTION REGISTER A (0X170, 0X1A0)                    | 69 |

| TABLE 5-32: DAC X CORRECTION REGISTER B (0X174, 0X1A4)                    | 69 |

| TABLE 5-33: DAC X CORRECTION REGISTER C (0X178, 0X1A8)                    | 69 |

| TABLE 5-34: DAC X CORRECTION REGISTER D (0X17C, 0X1AC)                    | 69 |

| TABLE 5-35: DAC X DATA REGISTER A & B (0X180, 0X1B0)                      | 70 |

| TABLE 5-36: DAC X DATA REGISTER C & D (0X184, 0X1B4)                      |    |

| TABLE 5-37: DAC X STATUS REGISTER (0X188, 0X1B8)                          | 72 |

| TABLE 5-38: DAC X MODE REGISTER (0X18C, 0X1BC)                            | 73 |

| TABLE 5-39 : D/A SEQUENCER CONTROL REGISTER (0X2E8)                       | 76 |

| TABLE 5-40 : D/A SEQUENCER STATUS REGISTER (0X2EC)                        |    |

| TABLE 5-41: D/A SEQUENCER NUMBER OF CONVERSIONS REGISTER (0X2F4)          | 79 |

| TABLE 5-42 : D/A SEQUENCER CONVERSION COUNT REGISTER (0X2F8)              |    |

| TABLE 5-43 : D/A SEQUENCER FIFO LEVEL REGISTER (0X2FC)                    |    |

| TABLE 5-44: D/A SEQUENCER DMA BUFFER BASE ADDRESS REGISTER (0X308)        | 80 |

| TABLE 5-45 : D/A SEQUENCER DMA BUFFER LENGTH REGISTER (0X30C)             | 80 |

| TABLE 5-46: D/A SEQUENCER DMA BUFFER NEXT ADDRESS REGISTER (0X310)        | 80 |

| TABLE 5-47: CONVERSION CLOCK 1 GENERATOR REGISTER (0X320)                 |    |

| TABLE 5-48: CONVERSION CLOCK 2 GENERATOR REGISTER (0X324)                 |    |

| TABLE 5-49: FRAME TRIGGER GENERATOR REGISTER (0X32C)                      |    |

| TABLE 5-50: FRAME TRIGGER GENERATOR REGISTER 2 (0X330)                    |    |

| TABLE 5-51: CONVERSION SIGNAL GENERATOR ENABLE REGISTER (0X33C)           | 83 |

| TABLE 5-52: CONVERSION SIGNAL GENERATOR OUTPUT DRIVER REGISTER (0X340)    | 84 |

| TABLE 5-53: CONVERSION SIGNAL SOURCE SELECTION REGISTER (0X344)           |    |

| TABLE 5-54: CONVERSION SIGNAL PATH CONFIGURATION EXAMPLES                 |    |

| TABLE 5-55: FRAME TIMER REGISTER (0X348)                                  |    |

| TABLE 5-56: DIO INPUT REGISTER (0X354)                                    |    |

| TABLE 5-57: DIO INPUT FILTER REGISTER (0X358)                             |    |

| TABLE 5-58: DIO OUTPUT REGISTER (0X35C)                                   | 88 |

| TABLE 5-59: DIO OUTPUT ENABLE REGISTER (0X360)                     | 89  |

|--------------------------------------------------------------------|-----|

| TABLE 5-60: INTERRUPT ENABLE REGISTER (0X36C)                      | 91  |

| TABLE 5-61: ERROR INTERRUPT ENABLE REGISTER (0X370)                | 92  |

| TABLE 5-62: DIO RISING EDGE INTERRUPT ENABLE REGISTER (0X374)      | 93  |

| TABLE 5-63: DIO FALLING EDGE INTERRUPT ENABLE REGISTER (0X378)     | 94  |

| TABLE 5-64: INTERRUPT STATUS REGISTER (0X384)                      | 96  |

| TABLE 5-65: ERROR INTERRUPT STATUS REGISTER (0X388)                | 98  |

| TABLE 5-66: DIO INTERRUPT STATUS REGISTER (0X38C)                  | 99  |

| TABLE 5-67: GLOBAL CONFIGURATION REGISTER (0X398)                  | 100 |

| TABLE 5-68: DIO PULL REFERENCE REGISTER (0X39C)                    | 101 |

| TABLE 5-69: P14 I/O PULL REFERENCE REGISTER (0X3A0)                | 101 |

| TABLE 5-70: CORRECTION DATA EEPROM CONTROL/STATUS REGISTER (0X3A4) | 102 |

| TABLE 5-71: TEMPERATURE SENSOR TRIGGER REGISTER (0X3A8)            | 103 |

| TABLE 5-72: TEMPERATURE SENSOR DATA REGISTER (0X3AC)               |     |

| TABLE 5-73: FIRMWARE VERSION REGISTER (0X3FC)                      |     |

| TABLE 7-1: UNIPOLAR VOLTAGE OUTPUT RANGES                          |     |

| TABLE 7-2: BIPOLAR VOLTAGE OUTPUT RANGES                           |     |

| TABLE 7-3: CURRENT OUTPUT RANGES                                   |     |

| TABLE 7-4: ANALOG OUTPUT TRANSFER FUNCTION                         |     |

| TABLE 8-1: ANALOG INPUT RANGES                                     |     |

| TABLE 8-2: A/D DATA CODING                                         |     |

| TABLE 9-1: D/A HOST MEMORY DATA BUFFER EXAMPLE                     |     |

| TABLE 9-2: MAX. A/D CONVERSION RATE                                |     |

| TABLE 9-3: A/D HOST MEMORY DATA BUFFER EXAMPLE                     |     |

| TABLE 9-4: FRAME TRIGGER TIMING PARAMETER                          |     |

| TABLE 10-1: FRONT I/O CONNECTOR TYPE                               |     |

| TABLE 10-2: FRONT I/O SIGNAL TYPES                                 |     |

| TABLE 10-3: FRONT I/O PIN ASSIGNMENT                               |     |

| TABLE 10-4: P14 REAR I/O CONNECTOR TYPE                            |     |

| TARLE 10-5 · P14 REAR I/O PIN ASSIGNMENT                           | 143 |

### 1 Product Description

The TPMC541 is a standard single-wide PCI Mezzanine Card (PMC) compatible module providing:

- A PCI Master capable 32 bit 33 MHz PCI interface

- 8 Tristate-Capable bi-directional 5V-tolerant LVTTL/TTL compatible General Purpose Digital I/O Lines (Front I/O)

- Up to 8 Single-Ended 16 bit Analog Outputs in (bipolar or unipolar) Voltage Mode or (unipolar)

Current Mode (Front I/O)

- Up to 32 Single-Ended or 16 Differential 16 bit bipolar Analog Inputs (Front I/O)

- Tristate-Capable bi-directional 5V-tolerant LVTTL/TTL compatible Digital I/O Lines for Conversion Control Signals (Conversion Clock, Frame Trigger) (Rear-I/O)

Figure 1-1: TPMC541 Block Diagram

#### Digital I/O

The TPMC541 features 8 tristate-capable bi-directional general purpose digital I/O lines at the front I/O connector. Each digital I/O line has a dedicated line transmitter with individual output enable control and a dedicated line receiver. The line receivers are always enabled, so the digital I/O line level can be monitored even when used as an output. Each digital I/O line input is capable of generating an interrupt triggered on rising edge, falling edge or both edges. Additionally, a debounce filter can be configured to get rid of bouncing on the digital I/O inputs. Each digital I/O line is ESD protected and features a  $4.7k\Omega$  pull resistor to a common reference. The common pull resistor reference is programmable by software to +3.3V, +5V or GND.

#### **Conversion Control Signals**

Conversion clock (conversion rate) and frame trigger signals may be generated on-board for internal use and may also be driven out on P14 rear I/O if the card is operating as a master card in a Multi-Board configuration. The conversion clock (conversion rate) and frame trigger signals may also be sourced externally via the P14 rear I/O interface if the card is operating as a slave card in a Multi-Board configuration.

#### **Analog Outputs**

The TPMC541R-10R order option provides 8 (eight) analog output channels while the TPMC541R-20R order option provides 4 (four) analog output channels.

Each individual D/A channel can be configured to operate in any of the following output ranges:

- 0V to 5V Voltage Range

- 0V to 6V Voltage Range

- 0V to 10V Voltage Range

- 0V to 12V Voltage Range

- ±5V Voltage Range

- ±6V Voltage Range

- ±10V Voltage Range

- ±12V Voltage Range

- 4mA to 20mA Current Range

- 0mA to 20mA Current Range

- 0mA to 24mA Current Range

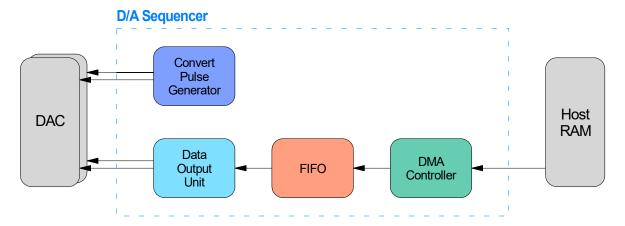

The TPMC541 provides a D/A Sequencer unit for performing a sequence of periodic simultaneous digital to analog conversions at a configurable conversion rate. In sequencer mode, the D/A conversion data is fetched from buffers in host memory via PCI Master DMA transfer and is temporarily stored in an on-board data buffer. The D/A Sequencer also provides a Frame Mode for repetitive frames of simultaneous D/A conversions upon a frame trigger signal event at a configurable frame rate

Besides the Sequencer Mode, D/A channel data can also be processed directly via the register interface (Manual Mode).

#### **Analog Inputs**

The Analog Devices ADAS3022 Analog-to-Digital Converter (ADC) device is used for the TPMC541 analog input sampling.

Each individual ADAS3022 device can be configured to either operate in Single-Ended Input Configuration (providing 8 single-ended A/D channels) or in Differential Input Configuration (providing 4 differential A/D channels).

The TPMC541R-10R order option provides four ADAS3022 devices, thus up to 32 single-ended or 16 differential analog inputs. The TPMC541-20R order option provides two ADAS3022 devices, thus up to 16 single-ended or 8 differential analog inputs.

Each ADC device configured for Single-Ended Input Configuration provides the following input voltage ranges (single-ended and referenced to ground): ±0.64V, ±1.28V, ±2.56V, ±5.12V, ±10.24V, ±12.288V.

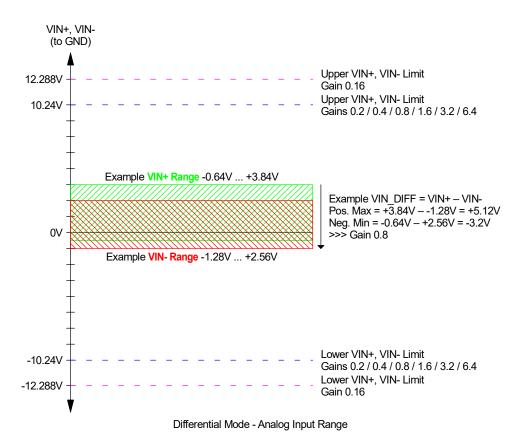

Each ADC device configured for Differential Input Configuration provides the following differential input voltage ranges: ±0.64V, ±1.28V, ±2.56V, ±5.12V, ±10.24V, ±20.48V, ±24.576V.

The ADAS3022 is a multiplexed ADC utilizing an embedded input channel multiplexer for connecting multiple analog input channels sequentially to a single integrated SAR ADC. Due to the multiplexed nature of the ADAS3022, the A/D conversions are being performed with a small delay between the input channels of the same ADAS3022 device (pseudo-simultaneous).

The TPMC541 provides an A/D Sequencer unit for performing a sequence of periodic analog to digital conversions at a configurable conversion rate. In sequencer mode, the A/D conversion data is temporarily stored in an on-board data buffer and then written to buffers in host memory by PCI master DMA transfer. The A/D Sequencer also provides a Frame Mode for repetitive frames of A/D conversion sequences upon a frame trigger signal event or at a configurable frame rate.

Besides the Sequencer Mode, A/D channel data can also be processed directly via the register interface (Manual Mode).

#### **Conversion Correction Data**

Each TPMC541 is factory calibrated. Conversion data correction values are determined during the factory acceptance test and are stored in an on-board serial EEPROM unique to each PMC module. These correction values may be used to perform a hardware correction for every individual D/A channel and output range and for every individual A/D channel and input range.

#### I/O Connector

The general purpose digital I/O signals, the analog output signals and the analog input signals are accessible on a 68 pos. Mini D Ribbon (MDR68) front connector.

# **2 Technical Specification**

| PMC Interface             | PMC Interface                                                                                                                                                                                                                                                                                         |  |  |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Mechanical Interface      | PCI Mezzanine Card (PMC) Interface confirming to IEEE P1386/P1386.1 ,Standard single-wide                                                                                                                                                                                                             |  |  |  |  |

| Electrical Interface      | PCI Rev. 3.0 compatible 33 MHz / 32 bit PCI Initiator/Target 3.3V and 5V PCI Signaling Voltage compatible                                                                                                                                                                                             |  |  |  |  |

| On Board Devices          |                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| FPGA                      | XC6SLX45-2FTG484I (Xilinx)                                                                                                                                                                                                                                                                            |  |  |  |  |

| Digital I/O               | 74LVT126 (NXP)                                                                                                                                                                                                                                                                                        |  |  |  |  |

| DAC                       | Order Options: TPMC541-10R: 2x AD5755-1 (Analog Devices) TPMC541-20R: 1x AD5755-1 (Analog Devices)                                                                                                                                                                                                    |  |  |  |  |

| ADC                       | Order Options: TPMC541-10R: 4x ADAS3022 (Analog Devices) TPMC541-20R: 2x ADAS3022 (Analog Devices)                                                                                                                                                                                                    |  |  |  |  |

| EEPROM                    | M93C86 (ST) 16kbit Serial EEPROM                                                                                                                                                                                                                                                                      |  |  |  |  |

| FPGA Configuration Memory | W25Q32 (Winbond) 32Mbit Serial SPI Flash                                                                                                                                                                                                                                                              |  |  |  |  |

| I/O Interface             |                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Digital I/O Channels      | 8 ESD Protected TTL/LVTTL Digital I/O Lines (Front I/O) 3.3V Driver, 5V tolerant Receiver, Individual Output Enable Control, Pull Resistor to common reference, Programmable common pull resistor reference (3.3V, 5V, GND) Up to 12mA Source Current and up to 6mA Sink Current per Digital I/O Line |  |  |  |  |

|                           | Order Options: TPMC541-10R: 8 Single-Ended 16 Bit D/A Channels TPMC541-20R: 4 Single-Ended 16 Bit D/A Channels Output range configurable per D/A channel. Simultaneous Conversion for all D/A Channels. Conversion Rate up to 38kSPS.                                                                 |  |  |  |  |

| D/A Channels              | Voltage Mode Ranges: 0V 5V, 0V 10V, -5V +5V, -10V +10V 0V 6V, 0V 12V, -6V +6V, -12V +12V (Over-ranges) Up to 10mA load current per Voltage Mode D/A Channel Current Mode Ranges: 4mA 20mA, 0mA 20mA, 0mA 24mA Max 680Ω load resistance per Current Mode D/A Channel                                   |  |  |  |  |

| A/D Channels            | Order Options: TPMC541-10R: 4x ADAS3022 ADC Device TPMC541-20R: 2x ADAS3022 ADC Device Input Configuration per ADC Device: 8x Single-Ended A/D Channels or 4x Differential A/D Channels A/D Channel Input Range Options: Single-Ended Input Voltage Ranges: ±0.64V, ±1.28V, ±2.56V, ±5.12V, ±10.24V, ±12.228V Differential Input Voltage Ranges: ±0.64V, ±1.28V, ±2.56V, ±5.12V, ±10.24V, ±20.48V, ±24.576V On-board analog input 1st order low-pass filter with -3dB cutoff frequency of approx. 105kHz on all A/D channels Max conversion Rate from 100ksps to 800ksps, depending on the number of active channels per ADC device. Pseudo-Simultaneous conversion for all A/D channels |                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| I/O Connectors          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Front I/O               | 68 pin Mini D Ribbon (MDR) (3M N10268-52E2PC or compatible)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| P14 Rear I/O            | 64 pin Mezzanine Connector (Molex 71436-2864 or compatible)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Physical Data           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Power Requirements      | Only the 5V PMC Power Supply is used TPMC541-10R: Typically 0.85A @ +5V DC without I/O Load TPMC541-20R: Typically 0.55A @ +5V DC without I/O Load I/O Load Calculation:  Add 0.005A @ +5V per active DIO Output Line Add 0.070A @ +5V per active D/A Voltage Output w/o Overrange Add 0.082A @ +5V per active D/A Voltage Output w/ Overrange Add approx. (IRANGE_MAX <sup>2</sup> * REXT) / 3V ampere @ +5V per active D/A Current Output                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Output                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Temperature Range       | Operating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -40°C to +85 °C (Forced air cooling is mandatory at ambient temperatures exceeding +40°C)                                                                                                                                                                                                                                                                                                                    |  |  |

| Temperature Range  MTBF | Operating  Storage  TPMC541-10  TPMC541-20  MTBF values sh MIL-HDBK-217f The MTBF calcu component supp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -40°C to +85 °C (Forced air cooling is mandatory at ambient temperatures exceeding +40°C) -40°C to +85 °C  OR: 165000h                                                                                                                                                                                                                                                                                       |  |  |

|                         | Operating  Storage  TPMC541-10  TPMC541-20  MTBF values sh MIL-HDBK-217f The MTBF calcu component supp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -40°C to +85 °C (Forced air cooling is mandatory at ambient temperatures exceeding +40°C)  -40°C to +85 °C  OR: 165000h  OR: 181000h  nown are based on calculation according to MIL-HDBK-217F and FNotice 2; Environment: GB 20°C.  Ilation is based on component FIT rates provided by the oliers. If FIT rates are not available, MIL-HDBK-217F and FNotice 2 formulas are used for FIT rate calculation. |  |  |

Table 2-1: Technical Specification

## 3 Handling and Operation Instructions

### 3.1 ESD Protection

This PMC module is sensitive to static electricity.

Packing, unpacking and all other module handling has to be done with the appropriate care.

### 3.2 Power Dissipation

This PMC module requires adequate forced air cooling!

**Attention:** Forced air cooling is mandatory at ambient temperatures exceeding 40°C!

### 3.3 Default Digital I/O Line State

The digital I/O lines are not actively driven after power-up / reset. However, each digital I/O line is connected to a common pull reference by way of a dedicated pull resistor.

The common pull reference is programmable (3.3V, 5V, GND) but is floating by default.

# 4 Address Map(s)

## 4.1 PCI Configuration Space

| PCI CFG<br>Register | Write '0' to all u        | Initial Values<br>(Hex Values) |                      |                |              |  |

|---------------------|---------------------------|--------------------------------|----------------------|----------------|--------------|--|

| Address             | 31 24                     | 23 16                          | 15 8                 | 7 0            | (HOX Values) |  |

| 0x00                | Devi                      | ce ID                          | Vend                 | lor ID         | 021D 1498    |  |

| 0x04                | Sta                       | atus                           | Com                  | mand           | 0280 0000    |  |

| 0x08                |                           | Class Code                     |                      | Revision ID    | 118000 00    |  |

| 0x0C                | not supported Header Type |                                | PCI Latency<br>Timer | not supported  | 00 00 00 00  |  |

| 0x10                |                           | Base Address R                 | egister 0 (BAR0)     |                | FFFFFC00     |  |

| 0x14                |                           | FFFFF800                       |                      |                |              |  |

| 0x18                |                           | 00000000                       |                      |                |              |  |

| 0x1C                |                           | 00000000                       |                      |                |              |  |

| 0x20                |                           |                                | 00000000             |                |              |  |

| 0x24                |                           |                                | 00000000             |                |              |  |

| 0x28                | PC                        | I CardBus Informa              | ation Structure Poir | nter           | 00000000     |  |

| 0x2C                | Subsy                     | stem ID                        | Subsystem            | Vendor ID      | s.b. 1498    |  |

| 0x30                |                           |                                | 00000000             |                |              |  |

| 0x34                |                           | 00000000                       |                      |                |              |  |

| 0x38                |                           | 00000000                       |                      |                |              |  |

| 0x3C                | Max_Lat                   | Min_Gnt                        | Interrupt Pin        | Interrupt Line | 00 00 01 00  |  |

| 0x40-<br>0xFF       |                           | 00000000                       |                      |                |              |  |

Table 4-1: PCI Configuration Space Header

| Vendor-ID: 0x149        |        | TEWS TECHNOLOGIES |  |

|-------------------------|--------|-------------------|--|

| Device-ID:              | 0x021D | TPMC541           |  |

| Subayatam ID:           | 0x000A | -10R Order Option |  |

| Subsystem-ID:           | 0x0014 | -20R Order Option |  |

| Subsystem<br>Vendor-ID: | 0x1498 | TEWS TECHNOLOGIES |  |

## 4.2 PCI Memory Space

The TPMC541 application registers are mapped into PCI Memory Space.

| Base<br>Address<br>Register<br>(BAR) | PCI Space<br>Mapping | Size<br>(Byte) | Port<br>Width<br>(Bit) | Endian<br>Mode | Description           |

|--------------------------------------|----------------------|----------------|------------------------|----------------|-----------------------|

| 0                                    | MEM                  | 1024           | 32                     | Little         | Register Space        |

| 1                                    | MEM                  | 2048           | 32                     | Little         | Correction Data Space |

Table 4-2: PCI Memory Address Spaces

### 4.2.1 Register Space

The Register Space is accessible via PCI Base Address Register 0 (BAR0).

ADC3, ADC4 and DAC2 registers are not available for the TPMC541-20R order option.

| PCI BAR 0<br>Offset | Description                        | Size (Bit)                                     |

|---------------------|------------------------------------|------------------------------------------------|

|                     | A/D Global Registers               | <u>,                                      </u> |

| 0x000               | Global ADC Control Register        | 32                                             |

| 0x004               | Global ADC Status Register         | 32                                             |

| 0x008               | Reserved                           | -                                              |

| 0x00C               | Reserved                           | -                                              |

|                     | A/D Device Registers               | <u>.</u>                                       |

| 0x010               | ADC1 Configuration Register        | 32                                             |

| 0x014               | Reserved                           | -                                              |

| 0x018               | ADC1 Correction Register Channel 0 | 32                                             |

| 0x01C               | ADC1 Correction Register Channel 1 | 32                                             |

| 0x020               | ADC1 Correction Register Channel 2 | 32                                             |

| 0x024               | ADC1 Correction Register Channel 3 | 32                                             |

| 0x028               | ADC1 Correction Register Channel 4 | 32                                             |

| 0x02C               | ADC1 Correction Register Channel 5 | 32                                             |

| 0x030               | ADC1 Correction Register Channel 6 | 32                                             |

| 0x034               | ADC1 Correction Register Channel 7 | 32                                             |

| 0x038               | ADC1 Data Register Channel 0/1     | 32                                             |

| 0x03C               | ADC1 Data Register Channel 2/3     | 32                                             |

| 0x040               | ADC1 Data Register Channel 4/5     | 32                                             |

| 0x044               | ADC1 Data Register Channel 6/7     | 32                                             |

| 0x048               | ADC1 Mode Register                 | 32                                             |

| 0x04C               | Reserved                           | -                                              |

| 0x050               | Reserved                           | -                                              |

| 0x054               | ADC2 Configuration Register        | 32                                             |

| 0x058               | Reserved                           | -                                              |

| PCI BAR 0<br>Offset | Description                        | Size (Bit) |

|---------------------|------------------------------------|------------|

| 0x05C               | ADC2 Correction Register Channel 0 | 32         |

| 0x060               | ADC2 Correction Register Channel 1 | 32         |

| 0x064               | ADC2 Correction Register Channel 2 | 32         |

| 0x068               | ADC2 Correction Register Channel 3 | 32         |

| 0x06C               | ADC2 Correction Register Channel 4 | 32         |

| 0x070               | ADC2 Correction Register Channel 5 | 32         |

| 0x074               | ADC2 Correction Register Channel 6 | 32         |

| 0x078               | ADC2 Correction Register Channel 7 | 32         |

| 0x07C               | ADC2 Data Register Channel 0/1     | 32         |

| 0x080               | ADC2 Data Register Channel 2/3     | 32         |

| 0x084               | ADC2 Data Register Channel 4/5     | 32         |

| 0x088               | ADC2 Data Register Channel 6/7     | 32         |

| 0x08C               | ADC2 Mode Register                 | 32         |

| 0x090               | Reserved                           | -          |

| 0x094               | Reserved                           | -          |

| 0x098               | ADC3 Configuration Register        | 32         |

| 0x09C               | Reserved                           | -          |

| 0x0A0               | ADC3 Correction Register Channel 0 | 32         |

| 0x0A4               | ADC3 Correction Register Channel 1 | 32         |

| 0x0A8               | ADC3 Correction Register Channel 2 | 32         |

| 0x0AC               | ADC3 Correction Register Channel 3 | 32         |

| 0x0B0               | ADC3 Correction Register Channel 4 | 32         |

| 0x0B4               | ADC3 Correction Register Channel 5 | 32         |

| 0x0B8               | ADC3 Correction Register Channel 6 | 32         |

| 0x0BC               | ADC3 Correction Register Channel 7 | 32         |

| 0x0C0               | ADC3 Data Register Channel 0/1     | 32         |

| 0x0C4               | ADC3 Data Register Channel 2/3     | 32         |

| 0x0C8               | ADC3 Data Register Channel 4/5     | 32         |

| 0x0CC               | ADC3 Data Register Channel 6/7     | 32         |

| 0x0D0               | ADC3 Mode Register                 | 32         |

| 0x0D4               | Reserved                           | -          |

| 0x0D8               | Reserved                           | -          |

| 0x0DC               | ADC4 Configuration Register        | 32         |

| 0x0E0               | Reserved                           | -          |

| 0x0E4               | ADC4 Correction Register Channel 0 | 32         |

| 0x0E8               | ADC4 Correction Register Channel 1 | 32         |

| 0x0EC               | ADC4 Correction Register Channel 2 | 32         |

| 0x0F0               | ADC4 Correction Register Channel 3 | 32         |

| 0x0F4               | ADC4 Correction Register Channel 4 | 32         |

| PCI BAR 0<br>Offset | Description                                    | Size (Bit) |

|---------------------|------------------------------------------------|------------|

| 0x0F8               | ADC4 Correction Register Channel 5             | 32         |

| 0x0FC               | ADC4 Correction Register Channel 6             | 32         |

| 0x100               | ADC4 Correction Register Channel 7             | 32         |

| 0x104               | ADC4 Data Register Channel 0/1                 | 32         |

| 0x108               | ADC4 Data Register Channel 2/3                 | 32         |

| 0x10C               | ADC4 Data Register Channel 4/5                 | 32         |

| 0x110               | ADC4 Data Register Channel 6/7                 | 32         |

| 0x114               | ADC4 Mode Register                             | 32         |

| 0x118               | Reserved                                       | -          |

| 0x11C               | Reserved                                       | -          |

|                     | A/D Sequencer Registers                        |            |

| 0x120               | A/D Sequencer Control Register                 | 32         |

| 0x124               | A/D Sequencer Status Register                  | 32         |

| 0x128               | Reserved                                       | -          |

| 0x12C               | A/D Sequencer Number of Conversions Register   | 32         |

| 0x130               | A/D Sequencer Conversion Count Register        | 32         |

| 0x134               | A/D Sequencer FIFO Level Register              | 32         |

| 0x138               | Reserved                                       | -          |

| 0x13C               | Reserved                                       | -          |

| 0x140               | A/D Sequencer DMA Buffer Base Address Register | 32         |

| 0x144               | A/D Sequencer DMA Buffer Length Register       | 32         |

| 0x148               | A/D Sequencer DMA Buffer Next Address Register | 32         |

| 0x14C               | A/D Sequencer DMA Status Base Address Register | 32         |

| 0x150               | Reserved                                       | -          |

| 0x154               | Reserved                                       | -          |

|                     | D/A Global Registers                           |            |

| 0x158               | Global DAC Control Register                    | 32         |

| 0x15C               | Global DAC Status Register                     | 32         |

| 0x160               | Reserved                                       | -          |

| 0x164               | Reserved                                       | -          |

|                     | D/A Device Registers                           |            |

| 0x168               | DAC1 Configuration Register                    | 32         |

| 0x16C               | Reserved                                       | -          |

| 0x170               | DAC1 Correction Register A                     | 32         |

| 0x174               | DAC1 Correction Register B                     | 32         |

| 0x178               | DAC1 Correction Register C                     | 32         |

| 0x17C               | DAC1 Correction Register D                     | 32         |

| 0x180               | DAC1 Data Register A & B                       | 32         |

| 0x184               | DAC1 Data Register C & D                       | 32         |

| PCI BAR 0<br>Offset | Description                                      | Size (Bit) |

|---------------------|--------------------------------------------------|------------|

| 0x188               | DAC1 Status Register                             | 32         |

| 0x18C               | DAC1 Mode Register                               | 32         |

| 0x190               | Reserved                                         | -          |

| 0x194               | Reserved                                         | -          |

| 0x198               | DAC2 Configuration Register                      | 32         |

| 0x19C               | Reserved                                         | -          |

| 0x1A0               | DAC2 Correction Register A                       | 32         |

| 0x1A4               | DAC2 Correction Register B                       | 32         |

| 0x1A8               | DAC2 Correction Register C                       | 32         |

| 0x1AC               | DAC2 Correction Register D                       | 32         |

| 0x1B0               | DAC2 Data Register A & B                         | 32         |

| 0x1B4               | DAC2 Data Register C & D                         | 32         |

| 0x1B8               | DAC2 Status Register                             | 32         |

| 0x1BC               | DAC2 Mode Register                               | 32         |

| 0x1C0               |                                                  |            |

|                     | Reserved                                         | -          |

| 0x2E4               |                                                  |            |

|                     | D/A Sequencer Registers                          |            |

| 0x2E8               | D/A Sequencer Control Register                   | 32         |

| 0x2EC               | D/A Sequencer Status Register                    | 32         |

| 0x2F0               | Reserved                                         | -          |

| 0x2F4               | D/A Sequencer Number Of Conversions Register     | 32         |

| 0x2F8               | D/A Sequencer Conversion Count Register          | 32         |

| 0x2FC               | D/A Sequencer FIFO Level Register                | 32         |

| 0x300               | Reserved                                         | -          |

| 0x304               | Reserved                                         | -          |

| 0x308               | D/A Sequencer DMA Buffer Base Address Register   | 32         |

| 0x30C               | D/A Sequencer DMA Buffer Length Register         | 32         |

| 0x310               | D/A Sequencer DMA Buffer Next Address Register   | 32         |

| 0x314               | Reserved                                         | -          |

| 0x318               | Reserved                                         | -          |

| 0x31C               | Reserved                                         | -          |

|                     | Conversion Signal Registers                      |            |

| 0x320               | Conversion Clock 1 Generator Register            | 32         |

| 0x324               | Conversion Clock 2 Generator Register            | 32         |

| 0x328               | Reserved                                         | -          |

| 0x32C               | Frame Trigger Generator Configuration Register 1 | 32         |

| 0x330               | Frame Trigger Generator Configuration Register 2 | 32         |

| 0x334               | Reserved                                         | -          |

| PCI BAR 0<br>Offset | Description                                        | Size (Bit) |

|---------------------|----------------------------------------------------|------------|

| 0x338               | Reserved                                           | -          |

| 0x33C               | Conversion Signal Generator Enable Register        | 32         |

| 0x340               | Conversion Signal Generator Output Driver Register | 32         |

| 0x344               | Conversion Signal Source Selection Register        | 32         |

| 0x348               | Frame Timer Register                               | 32         |

| 0x34C               | Reserved                                           | -          |

| 0x350               | Reserved                                           | -          |

|                     | Digital I/O Registers                              |            |

| 0x354               | DIO Input Register                                 | 32         |

| 0x358               | DIO Input Filter Register                          | 32         |

| 0x35C               | DIO Output Register                                | 32         |

| 0x360               | DIO Output Enable Register                         | 32         |

| 0x364               | Reserved                                           | -          |

| 0x368               | Reserved                                           | -          |

|                     | Interrupt Registers                                |            |

| 0x36C               | Interrupt Enable Register                          | 32         |

| 0x370               | Error Interrupt Enable Register                    | 32         |

| 0x374               | DIO Rising Edge Interrupt Enable Register          | 32         |

| 0x378               | DIO Falling Edge Interrupt Enable Register         | 32         |

| 0x37C               | Reserved                                           | -          |

| 0x380               | Reserved                                           | -          |

| 0x384               | Interrupt Status Register                          | 32         |

| 0x388               | Error Interrupt Status Register                    | 32         |

| 0x38C               | DIO Interrupt Status Register                      | 32         |

| 0x390               | Reserved                                           | -          |

| 0x394               | Reserved                                           | -          |

|                     | Other Registers                                    |            |

| 0x398               | Global Configuration Register                      | 32         |

| 0x39C               | DIO Pull Reference Register                        | 32         |

| 0x3A0               | P14 I/O Pull Reference Register                    | 32         |

| 0x3A4               | Correction EEPROM Control/Status Register          | 32         |

| 0x3A8               | Temperature Sensor Trigger Register                | 32         |

| 0x3AC               | Temperature Sensor Data Register                   | 32         |

| 0x3B0               |                                                    |            |

| <br>0x3F8           | Reserved                                           | -          |

| 0x3FC               | Firmware Version Register                          | 32         |

Table 4-3: Register Space Address Map

### 4.2.2 Correction Data Space

The Correction Data space is accessible via PCI Base Address Register 1 (BAR1).

Correction values for each input range of each ADC device channel and for each output range of each DAC device channel are determined and programmed at factory and can be read from this space.

The correction values are stored in an on-board serial EEPROM. The correction values are loaded from the EEPROM after power-up and/or PCI reset and are accessible in the Correction Data Space as indicated by the EEBSY bit in the Correction Data EEPROM Control/Status Register. See also the Correction Data EEPROM Control/Status Register description for more information.

For using the HW data correction, SW must read the appropriate correction values from the correction data space (depending on the actual range configuration of the A/D and D/A channels) and write the correction values to the corresponding ADC and DAC Correction Registers.

Devices ADC 3, ADC 4 and DAC 2 are not present on the TPMC541-20R order option.

| PCI BAR1<br>Offset | Description                                                          | Size (Bit) |

|--------------------|----------------------------------------------------------------------|------------|

|                    | ADC Differential Mode A/D Channel ±24.576V Range                     |            |

| 0x000              | ADC 1 Differential Channel 0, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x002              | ADC 1 Differential Channel 0, ±24.576V Range, Gain <sub>Corr</sub>   | 16         |

| 0x004              | ADC 1 Differential Channel 1, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x006              | ADC 1 Differential Channel 1, ±24.576V Range, Gain <sub>Corr</sub>   | 16         |

| 0x008              | ADC 1 Differential Channel 2, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x00A              | ADC 1 Differential Channel 2, ±24.576V Range, Gain <sub>Corr</sub>   | 16         |

| 0x00C              | ADC 1 Differential Channel 3, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x00E              | ADC 1 Differential Channel 3, ±24.576V Range, Gain <sub>Corr</sub>   | 16         |

| 0x010              | ADC 2 Differential Channel 0, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x012              | ADC 2 Differential Channel 0, ±24.576V Range, Gain <sub>Corr</sub>   | 16         |

| 0x014              | ADC 2 Differential Channel 1, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x016              | ADC 2 Differential Channel 1, ±24.576V Range, Gaincorr               | 16         |

| 0x018              | ADC 2 Differential Channel 2, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x01A              | ADC 2 Differential Channel 2, ±24.576V Range, Gain <sub>Corr</sub>   | 16         |

| 0x01C              | ADC 2 Differential Channel 3, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x01E              | ADC 2 Differential Channel 3, ±24.576V Range, Gain <sub>Corr</sub>   | 16         |

| 0x020              | ADC 3 Differential Channel 0, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x022              | ADC 3 Differential Channel 0, ±24.576V Range, Gain <sub>Corr</sub>   | 16         |

| 0x024              | ADC 3 Differential Channel 1, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x026              | ADC 3 Differential Channel 1, ±24.576V Range, Gain <sub>Corr</sub>   | 16         |

| 0x028              | ADC 3 Differential Channel 2, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x02A              | ADC 3 Differential Channel 2, ±24.576V Range, Gain <sub>Corr</sub>   | 16         |

| 0x02C              | ADC 3 Differential Channel 3, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x02E              | ADC 3 Differential Channel 3, ±24.576V Range, Gain <sub>Corr</sub>   | 16         |

| 0x030              | ADC 4 Differential Channel 0, ±24.576V Range, Offset <sub>Corr</sub> | 16         |

| 0x032              | ADC 4 Differential Channel 0, ±24.576V Range, Gaincorr               | 16         |

| 0x034 | ADC 4 Differential Channel 1, ±24.576V Range, Offset <sub>Corr</sub> | 16 |

|-------|----------------------------------------------------------------------|----|

| 0x036 | ADC 4 Differential Channel 1, ±24.576V Range, GainCorr               | 16 |

| 0x038 | ADC 4 Differential Channel 2, ±24.576V Range, OffsetCorr             | 16 |

| 0x03A | ADC 4 Differential Channel 2, ±24.576V Range, Gain <sub>Corr</sub>   | 16 |

| 0x03C | ADC 4 Differential Channel 3, ±24.576V Range, OffsetCorr             | 16 |

| 0x03E | ADC 4 Differential Channel 3, ±24.576V Range, GainCorr               | 16 |

| 0x040 | Reserved                                                             | 16 |

| 0x042 | Reserved                                                             | 16 |

| 0x044 | Reserved                                                             | 16 |

| 0x046 | Reserved                                                             | 16 |

| 0x048 | Reserved                                                             | 16 |

| 0x04A | Reserved                                                             | 16 |

| 0x04C | Reserved                                                             | 16 |

| 0x04E | Reserved                                                             | 16 |

| 0x050 | Reserved                                                             | 16 |

| 0x052 | Reserved                                                             | 16 |

| 0x054 | Reserved                                                             | 16 |

| 0x056 | Reserved                                                             | 16 |

| 0x058 | Reserved                                                             | 16 |

| 0x05A | Reserved                                                             | 16 |

| 0x05C | Reserved                                                             | 16 |

| 0x05E | Reserved                                                             | 16 |

| 0x060 | Reserved                                                             | 16 |

| 0x062 | Reserved                                                             | 16 |

| 0x064 | Reserved                                                             | 16 |

| 0x066 | Reserved                                                             | 16 |

| 0x068 | Reserved                                                             | 16 |

| 0x06A | Reserved                                                             | 16 |

| 0x06C | Reserved                                                             | 16 |

| 0x06E | Reserved                                                             | 16 |

| 0x070 | Reserved                                                             | 16 |

| 0x072 | Reserved                                                             | 16 |

| 0x074 | Reserved                                                             | 16 |

| 0x076 | Reserved                                                             | 16 |

| 0x078 | Reserved                                                             | 16 |

| 0x07A | Reserved                                                             | 16 |

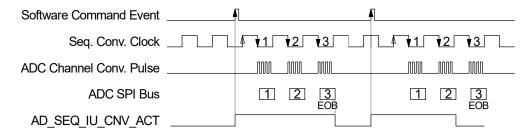

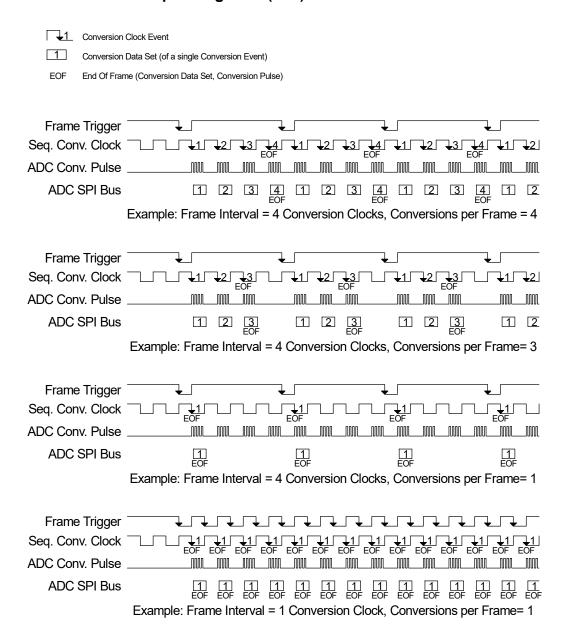

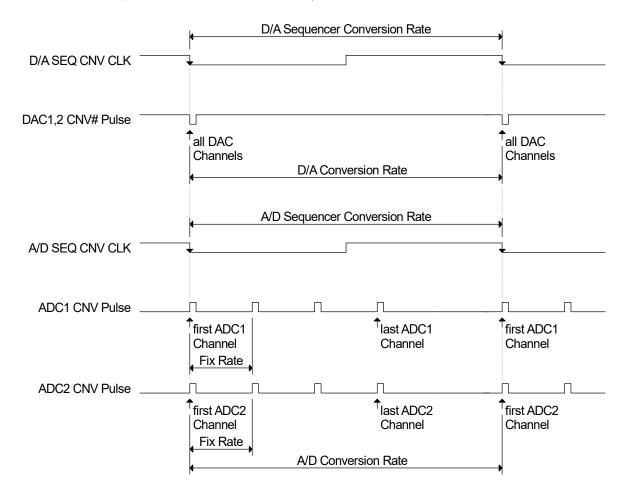

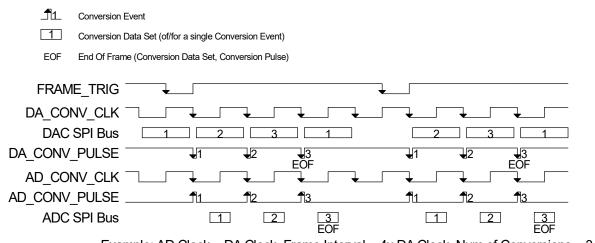

| 0x07C | Reserved                                                             | 16 |