## The Embedded I/O Company

# **TPMC151**

## 4 Channel Resolver or LVDT/RVDT-to-Digital Converter

Version 1.0

## **User Manual**

Issue 1.0.2 August 2024

#### TPMC151-10R

4 Channel Resolver or LVDT/RVDT-to-Digital Converter

(RoHS compliant)

#### **TPMC151-20R**

2 Channel Resolver or LVDT/RVDT-to-Digital Converter, 2 Channel Synchro-to-Digital Converter

(RoHS compliant)

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However, TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### ©2024 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description                              | Date         |

|-------|------------------------------------------|--------------|

| 1.0.0 | Initial issue                            | January 2024 |

| 1.0.1 | Added -20R variant                       | May 2024     |

| 1.0.2 | Changed I/O connector to 50-pin MDR type | August 2024  |

## **Table of Contents**

| 1 | PRO        | DUCT [                   | DESCRIPTION                                    | 8  |

|---|------------|--------------------------|------------------------------------------------|----|

| 2 | TEC        | HNICAL                   | _ SPECIFICATION                                | 9  |

| 3 | HAN        | IDLING.                  | AND OPERATION INSTRUCTIONS                     | 11 |

|   | 3.1        | ESD Pro                  | otection                                       | 11 |

|   | 3.2        |                          | Dissipation                                    |    |

| 4 |            |                          | D DEFINITIONS                                  |    |

| _ |            |                          |                                                |    |

|   | 4.1        |                          | r Bit Access Types                             |    |

|   | 4.2<br>4.3 | •                        | onventions<br>V                                |    |

| _ |            |                          | •                                              |    |

| 5 |            |                          | ACE                                            |    |

|   | 5.1        |                          | ntifiers                                       |    |

|   | 5.2        |                          | e Address Register Configuration               |    |

|   | 5.3        |                          | Registers                                      |    |

|   | 5.3.       |                          | gister Map                                     |    |

|   | 5.3.       |                          | gister Description                             |    |

|   |            |                          | Channel [x] Excitation Register                |    |

|   |            |                          | Channel [x] Data Register with Status          |    |

|   |            |                          | Channel [x] Data Register with Velocity        |    |

|   |            |                          | Combined Data Register Channel 2 & 1 / 4 & 3   |    |

|   |            |                          | Combined Status Register Channel 2 & 1 / 4 & 3 |    |

|   |            |                          | AFE Control Register                           |    |

|   | 5.3        |                          | AFE Status Register                            |    |

|   | 5.3        | 3.2.9 I                  | Input Range Register                           | 20 |

|   |            |                          | Channel [x] Ring Buffer Control Register       |    |

|   |            |                          | Channel [x] Ring Buffer Status Register        |    |

|   |            |                          | Channel [x] Ring Buffer Data Register          |    |

|   |            |                          | Global Registers                               |    |

|   |            | 5.3.2.13.1<br>5.3.2.13.2 | 5                                              |    |

|   |            | 5.3.2.13.2<br>5.3.2.13.3 |                                                |    |

|   |            | 5.3.2.13.4<br>5.3.2.13.4 |                                                |    |

|   |            | 5.3.2.13.5               |                                                |    |

|   |            | 5.3.2.13.6               | 3                                              |    |

|   | !          | 5.3.2.13.7               | <del>-</del>                                   |    |

|   | ;          | 5.3.2.13.8               |                                                |    |

|   |            | 5.3.2.13.9               |                                                |    |

|   |            | 5.3.2.13.1               | 0 Firmware Identification Register             | 27 |

| 6 | FUN        | CTIONA                   | AL DESCRIPTION                                 | 28 |

|   | 6.1        | Resolve                  | r                                              | 28 |

|   | 6.1.       |                          | solver Wiring Modes                            |    |

|   | 6.1.       |                          | sign Procedure for Resolver                    |    |

|   | 6.2        |                          |                                                |    |

|   | 6.2.       |                          | OT Wiring Modes                                |    |

|   | _          |                          | Differential Wiring                            |    |

|   | _          |                          | Ratiometric Wiring                             |    |

|   | 6.2.       |                          | sign Procedure for LVDT                        |    |

|   | 6.3        | •                        | )                                              |    |

|   | 6.3.       | .ı Syn                   | nchro Wiring Modes                             | 32 |

|     | 6.3 | .2 Design Procedure for Synchro    | 32 |

|-----|-----|------------------------------------|----|

| 6   |     | Interval Timer                     |    |

| 6   | 6.5 | Ring Buffer                        | 33 |

| 7 F | PIN | ASSIGNMENT - I/O CONNECTOR         | 34 |

| 7   | 7.1 | Maximum Voltage Ratings            | 34 |

|     |     | Front Panel I/O Connector          |    |

| 7   | 7.3 | TPMC151-10R Front Panel I/O Pinout | 35 |

| 7   | 7.4 | TPMC151-20R Front Panel I/O Pinout | 36 |

# **List of Figures**

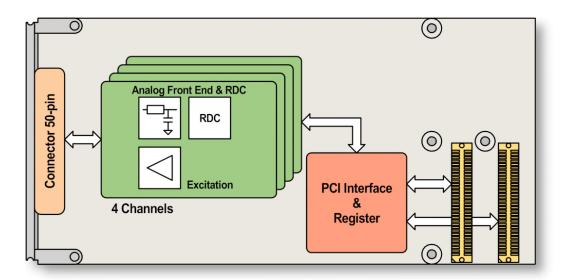

| FIGURE 1-1: BLOCK DIAGRAM TPMC151-10R                                      | 8  |

|----------------------------------------------------------------------------|----|

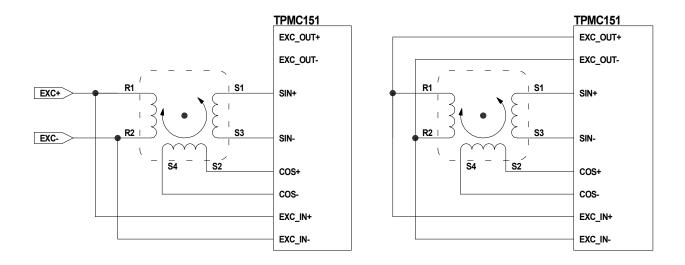

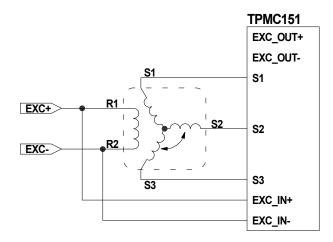

| FIGURE 6-1: RESOLVER WIRING WITH EXTERNAL AND INTERNAL EXCITATION          | 28 |

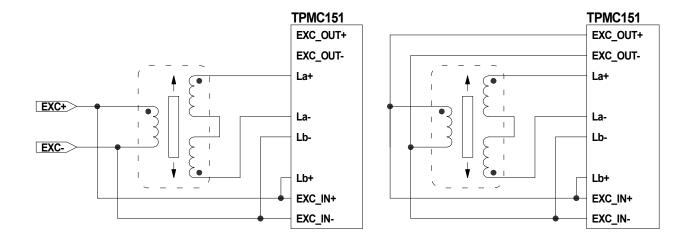

| FIGURE 6-2: LVDT DIFFERENTIAL WIRING WITH EXTERNAL AND INTERNAL EXCITATION | 29 |

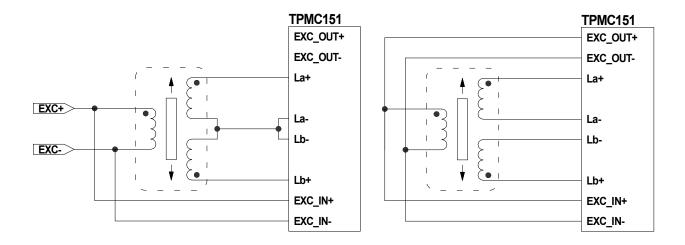

| FIGURE 6-3: LVDT 5-WIRE AND 6-WIRE RATIOMETRIC WIRING EXAMPLES             | 30 |

| FIGURE 6-4: SYNCHRO WIRING WITH EXTERNAL EXCITATION                        | 32 |

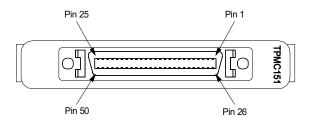

| FIGURE 7-1: FRONT PANEL I/O CONNECTOR PIN NUMBERING                        | 34 |

|                                                                            |    |

|                                                                            |    |

| List of Tables                                                             |    |

| TABLE 2-1: TECHNICAL SPECIFICATION                                         | 10 |

| TABLE 5-1: PCI IDENTIFIERS                                                 | 13 |

| TABLE 5-2: PCI BASE ADDRESS REGISTERS                                      | 13 |

| TABLE 5-3: INTERNAL REGISTERS                                              | 14 |

| TABLE 5-4: CHANNEL [X] EXCITATION REGISTER                                 | 15 |

| TABLE 5-5: CHANNEL [X] DATA REGISTER WITH STATUS                           | 16 |

| TABLE 5-6: CHANNEL [X] DATA REGISTER WITH VELOCITY                         | 17 |

| TABLE 5-7: CHANNEL [X] DATA REGISTER WITH SAMPLE INDEX                     | 17 |

| TABLE 5-8: COMBINED DATA REGISTER CHANNEL 2 & 1 / 4 & 3                    | 17 |

| TABLE 5-9: COMBINED STATUS REGISTER CHANNEL 2 & 1 / 4 & 3                  | 18 |

| TABLE 5-10: AFE CONTROL REGISTER                                           | 18 |

| TABLE 5-11: AFE STATUS REGISTER                                            | 19 |

| TABLE 5-12: INPUT RANGES                                                   | 20 |

| TABLE 5-13: INPUT RANGE REGISTER                                           | 20 |

| TABLE 5-14: CHANNEL [X] RING BUFFER CONTROL REGISTER                       | 21 |

| TABLE 5-15: CHANNEL [X] RING BUFFER STATUS REGISTER                        | 22 |

| TABLE 5-16: CHANNEL [X] RING BUFFER DATA REGISTER                          | 22 |

| TABLE 5-17: GLOBAL CONTROL REGISTER                                        | 23 |

| TABLE 5-18: STATUS REGISTER                                                | 24 |

| TABLE 5-19: INTERRUPT ENABLE REGISTER                                      | 25 |

| TABLE 5-20: INTERVAL TIMER CONTROL REGISTER                                | 26 |

| TABLE 5-21: INTERVAL TIMER PRELOAD REGISTER                                | 26 |

| TABLE 5-22: INTERVAL TIMER DATA REGISTER                                   | 26 |

| TABLE 5-23: BOARD HEALTH REGISTER                                          | 27 |

| TABLE 5-24: SCRATCHPAD REGISTER                                            | 27 |

| TABLE 5-25: FIRMWARE IDENTIFICATION REGISTER                               |    |

| TABLE 6-1: EXAMPLE RESOLVER DESIGN PARAMETERS                              | 28 |

| TABLE 6-2: AVAILABLE INPUT RANGES                                          |    |

| TABLE 6-3: AVAILABLE INPUT RANGES                                          |    |

| TABLE 6-4: EXAMPLE LVDT DESIGN PARAMETERS                                  | 31 |

| TABLE 6-5: TPMC151-20R SYNCHRO INPUT RANGES                      | 32 |

|------------------------------------------------------------------|----|

| TABLE 6-6: INTERVAL TIMER CLOCK PERIODS                          | 33 |

| TABLE 6-7: INTERVAL TIMER TIME BASES                             | 33 |

| TABLE 7-1: MAXIMUM VOLTAGE RATINGS                               | 34 |

| TABLE 7-2: TPMC151-10R PIN ASSIGNMENT FRONT PANEL I/O CONNECTOR  | 35 |

| TABLE 7-3 : TPMC151-20R PIN ASSIGNMENT FRONT PANEL I/O CONNECTOR | 36 |

## 1 Product Description

The TPMC151 is a standard single-width 32-bit PMC module and supports a 33 MHz / 32-bit universal (5 V / 3.3 V) PCI interface.

The TPMC151-10R provides 4 channels of Resolver or LVDT/RVDT to Digital Converter with 16-bit resolution. It accepts input signals up to 12  $V_{RMS}$ , with frequencies ranging from 1 kHz to 20 kHz and allows tracking rates up to  $\frac{1}{4}$  of the excitation frequency (i.e. 10 kHz -> 2500 rps). The converter provides a digital angle, respectively stroke value, and a digital velocity value. For LVDT/RVDT differential and ratiometric sensor configuration is supported.

The TPMC151 provides individual excitation outputs with software selectable excitation frequency and output voltage swing for each channel. Adjustable frequency is ranging from 1 kHz to 20 kHz and the output voltage range is 0 to 12 V<sub>RMS</sub> with up to 100 mA. No external power supply is required. Alternatively, an external excitation can be used.

The TPMC151-20R replaces two resolver channels with two Synchro-to-Digital Converter channels. For Synchro channels the excitation output is not available and an external excitation must be used. Synchro channels accept inputs signals up to 28 V<sub>RMS</sub>, with frequencies ranging from 400 Hz to 20 kHz.

All TPMC151 signals are accessible through an 50-pin MDR type front I/O connector.

Software Support (TPMC151-SW-xx) for different operating systems is available.

Figure 1-1: Block Diagram TPMC151-10R

# 2 Technical Specification

| PMC Interface        |                                                                                |  |  |  |

|----------------------|--------------------------------------------------------------------------------|--|--|--|

| Mechanical Interface | PCI Mezzanine Card (PMC) Interface Single Size (149 mm x 74 mm)                |  |  |  |

| Electrical Interface | PCI Rev. 3.0 compliant 33 MHz / 32-bit PCI 3.3 V and 5 V PCI Signaling Voltage |  |  |  |

| On Board Devices                           |         |  |  |

|--------------------------------------------|---------|--|--|

| PCI Target Chip Artix-7 FPGA with PCI core |         |  |  |

| Analog Front End                           | AD7606C |  |  |

| I/O Interface                      |                                                                                                        |  |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| Number of Channels                 | 4                                                                                                      |  |  |  |

| Supported Sensor Configuration     | Resolver LVDT/RVDT: Differential ("4-wire") and Ratiometric ("6-wire" or "5-wire") Synchro (-20R only) |  |  |  |

| <b>Excitation Output</b>           | 0-12 V <sub>RMS</sub> , up to 100 mA                                                                   |  |  |  |

| <b>Excitation Output Frequency</b> | 1-20 kHz                                                                                               |  |  |  |

| Excitation Input                   | RDC / LVDT Channels: 0-12 V <sub>RMS</sub><br>Synchro Channels: 0-28 V <sub>RMS</sub>                  |  |  |  |

| Excitation Input Frequency         | RDC / LVDT Channels: 1-20 kHz<br>Synchro Channels: 0.4-20 kHz                                          |  |  |  |

| Sensor Input Voltage               | RDC / LVDT Channels: 0-12 V <sub>RMS</sub><br>Synchro Channels: 0-28 V <sub>RMS</sub>                  |  |  |  |

| Resolution                         | Angle/Stroke: 16-Bit<br>Velocity: 14-Bit                                                               |  |  |  |

| Tracking Rate                      | 1/4 Excitation Frequency                                                                               |  |  |  |

| Accuracy                           | RDC: Up to 1.5 arcmin  RDC Velocity: Up to ±0.5 %  LVDT/RVDT: Up to ±0.06 %  Synchro: Up to 4 arcmin   |  |  |  |

| Physical Data      |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Power Requirements | 180 mA typical @ +5V (no load on Excitation Outputs) 600 mA @ +5V (All 4 EXC outputs driving 3 V <sub>RMS</sub> @ 20 mA) 1800 mA @ +5V (All 4 EXC outputs driving 12 V <sub>RMS</sub> @ 80 mA) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Temperature Range  | Operating<br>Storage                                                                                                                                                                           | -40°C to +85°C<br>-40°C to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| MTBF               | TPMC151-20<br>MTBF values sh<br>MIL-HDBK-217F<br>The MTBF calcu<br>component supp                                                                                                              | DR: $682000 \text{ h}$ DR: $463000 $ |  |  |

| Humidity           | 5 – 95 % non-condensing                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Weight             | 73 g                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

Table 2-1: Technical Specification

# 3 Handling and Operation Instructions

## 3.1 ESD Protection

This PMC module is sensitive to static electricity.

Packing, unpacking and all other module handling has to be done with appropriate care.

## 3.2 Power Dissipation

When using the excitation output, this PMC module requires adequate forced air cooling!

## 4 Terms and Definitions

## 4.1 Register Bit Access Types

| Register Bit Access<br>Type |            | Description                                   |  |  |  |

|-----------------------------|------------|-----------------------------------------------|--|--|--|

| R                           | Read       | The bit is readable by software               |  |  |  |

| R/W                         | Read/Write | The bit is readable and writeable by software |  |  |  |

| R/C                         | Read/Clear | The bit is readable by software               |  |  |  |

|                             |            | The bit is set by firmware                    |  |  |  |

|                             |            | Software may clear the bit by writing a '1'   |  |  |  |

| R/S                         | Read/Set   | The bit is readable by software               |  |  |  |

|                             |            | Software may set this bit to '1'              |  |  |  |

|                             |            | The bit is cleared by firmware                |  |  |  |

When reading reserved register bits, the read value is undefined.

For future software compatibility: For register write access, reserved bits shall be written '0'.

## 4.2 Style Conventions

Hexadecimal characters are specified with prefix 0x (i.e. 0x029E).

For signals on hardware products, "Active Low" is represented by the signal name with an added # (i.e. IP\_RESET#).

## 4.3 Glossary

AFE Analog Front End

LVDT Linear Variable Differential Transformer

RDC Resolver to Digital Converter. Throughout this document "RDC" is used as "Resolver or LVDT/RVDT-to-Digital Converter"

RVDT Rotary Variable Differential Transformer. Since RVDTs works according to the same principle as LVDTs, through this document "LVDT" means "LVDT and/or RVDT"

## 5 PCI Interface

## 5.1 PCI Identifiers

| Vendor-ID           | 0x1498 (TEWS Technologies)              |  |  |

|---------------------|-----------------------------------------|--|--|

| Device-ID           | 0x0097 (TPMC151)                        |  |  |

| Class Code          | 0x118000 (Other data acquisition/signal |  |  |

|                     | processing controllers)                 |  |  |

| Subsystem Vendor-ID | 0x1498 (TEWS Technologies)              |  |  |

| Subsystem Device-ID | 0x000A (TPMC151-10R)                    |  |  |

|                     | 0x0014 (TPMC151-20R)                    |  |  |

Table 5-1: PCI Identifiers

## **5.2 PCI Base Address Register Configuration**

| PCI Base Address Register<br>(Offset in PCI<br>Configuration Space) | PCI<br>Space<br>Mapping | Size<br>(Byte) | Port<br>Width<br>(Bit) | Endian<br>Mode | Description        |

|---------------------------------------------------------------------|-------------------------|----------------|------------------------|----------------|--------------------|

| 0 (0x10)                                                            | MEM                     | 512            | 32                     | Little         | Internal Registers |

Table 5-2: PCI Base Address Registers

## 5.3 Internal Registers

Addresses and register bits marked as "reserved" should be written as '0'. Read values can be arbitrary and should not be relied upon.

## 5.3.1 Register Map

| PCI Base Address<br>Register 0 Offset | Description                               | Size<br>(Bit) |

|---------------------------------------|-------------------------------------------|---------------|

| 0x000                                 | Channel 1 Excitation Register             | 32            |

| 0x004                                 | Channel 1 Data Register with Status       | 32            |

| 0x008                                 | Channel 1 Data Register with Velocity     | 32            |

| 0x00C                                 | Channel 1 Data Register with Sample Index | 32            |

| 0x010-0x01C                           | Channel 2 (same as for Channel 1)         | 4x32          |

| 0x020-0x02C                           | Channel 3 (same as for Channel 1)         | 4x32          |

| 0x030-0x03C                           | Channel 4 (same as for Channel 1)         | 4x32          |

| 0x040                                 | Combined Data Register 2 & 1              | 32            |

| 0x044                                 | Combined Status Register 2 & 1            | 32            |

| 0x048                                 | Combined Data Register 4 & 3              | 32            |

| 0x04C                                 | Combined Status Register 4 & 3            | 32            |

| 0x050                                 | AFE Control                               | 32            |

| 0x054                                 | AFE Status                                | 32            |

| PCI Base Address<br>Register 0 Offset | Description                            | Size<br>(Bit) |

|---------------------------------------|----------------------------------------|---------------|

| 0x058                                 | Input Range Register                   | 32            |

| 0x05C-0x08C                           | reserved                               | -             |

| 0x80                                  | Channel 1 Ring Buffer Control Register | 32            |

| 0x84                                  | Channel 1 Ring Buffer Status Register  | 32            |

| 0x88                                  | Channel 1 Ring Buffer Data Register    | 32            |

| 0x8C                                  | reserved                               | 32            |

| 0x090-0x09C                           | Channel 2 (same as for Channel 1)      | 4x32          |

| 0x0A0-0x0AC                           | Channel 3 (same as for Channel 1)      | 4x32          |

| 0x0B0-0x0BC                           | Channel 4 (same as for Channel 1)      | 4x32          |

|                                       | Global Registers                       | ·             |

| 0x0C0                                 | Global Control Register                | 32            |

| 0x0C4                                 | Status Register                        | 32            |

| 0x0C8                                 | Interrupt Enable Register              | 32            |

| 0x0CC                                 | Interrupt Status Register              | 32            |

| 0x0D0-0x0DC                           | reserved                               | -             |

| 0x0E0                                 | Interval Timer Control Register        | 32            |

| 0x0E4                                 | Interval Timer Preload Register        | 32            |

| 0x0E8                                 | Interval Timer Data Register           | 32            |

| 0x0EC                                 | reserved                               | -             |

| 0x0F0                                 | reserved                               | -             |

| 0x0F4                                 | Board Health Register                  | 32            |

| 0x0F8                                 | Scratchpad Register                    | 32            |

| 0x0FC                                 | Firmware Version Register              | 32            |

| 0x100-0x1FC                           | reserved                               | -             |

Table 5-3: Internal Registers

## 5.3.2 Register Description

Most registers described here are individual for each sensor. These are readily identifiable by a tailing "[x]".

#### 5.3.2.1 Channel [x] Excitation Register

| Bit   | Symbol      | Description                                                                                                                                                                                                                                          | Access | Reset<br>Value |

|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:16 | EXC<br>FREQ | Excitation Frequency The Excitation Frequency on the x_EXC_OUT pins will be this value in Hz. Valid values are from 0x03E8 (= 1 kHz) to 0x4E20 (=20 kHz)                                                                                             |        | 0x0000         |

| 15:8  | EXC<br>VOLT | Excitation Voltage The Excitation Voltage (the differential voltage between the [x]_EXC_OUT+ and [x]_EXC_OUT- pins) will be this value x 0,05 V <sub>RMS</sub> . Useful values are from 0x28 (= 2 V <sub>RMS</sub> ) to 0xF0 (=12 V <sub>RMS</sub> ) |        | 0x00           |

| 7:1   | -           | Reserved                                                                                                                                                                                                                                             | -      | 0              |

| 0     | EXC<br>ENA  | Excitation Enable Set to '1' to enable the Excitation. This enables the frequency generation and the output amplifier. This bit is automatically reset when AMP OT event was registered.                                                             | R/W    | 0              |

Table 5-4: Channel [x] Excitation Register

#### 5.3.2.2 Channel [x] Data Register with Status

The status bits in this register represent the actual status valid for the ANGLE STROKE value in this register. Status bits may be short-lived and volatile. To provide a way to catch intermittently states the "Status Register" provides mirrors of most of the status bits that are "sticky", since they are latched until reset.

| Bit   | Symbol       | Description                                                                                                                                                                                                                                                                                                                                                         | Access       | Reset<br>Value |

|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

| 31:25 | -            | Reserved, always reads as '0'                                                                                                                                                                                                                                                                                                                                       | -            | 0              |

| 24    | AMP<br>OT    | '1' = Excitation Output Overtemperature Flag The excitation amplifier signaled an overtemperature condition. This resets the EXC ENA bit in the "Channel [x] Excitation Register", so the excitation output is disabled. This bit is cleared when the excitation is enabled again. Persisting overtemperature conditions will set this bit immediately back to '1'. | R            | 0              |

| 23    | INIT<br>DONE | '1' = RDC initialization done & output data is valid                                                                                                                                                                                                                                                                                                                | is valid R 0 |                |

| 22    | LOF          | '1' = RDC entered low frequency mode R This bit is set when the Excitation frequency is lower than 4 kHz                                                                                                                                                                                                                                                            |              | 0              |

| Bit  | Symbol          | Description                                                                                                                                                                                                                                                                                                                                         | Access | Reset<br>Value |

|------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 21   | EXC<br>HIGH     | '1' = Excitation Frequency too high,  f <sub>EXC</sub> > 20 kHz  If this bit is set while EXC LOW is also set, then the frequency is within limits, but not stable                                                                                                                                                                                  |        | 0              |

| 20   | EXC<br>LOW      | '1' = Excitation Frequency too low  f <sub>EXC</sub> < 400 Hz in "Synchro"-mode or f <sub>EXC</sub> < 1 kHz in all other modes.  If this bit is set while EXC HIGH is also set, then the frequency is within limits, but not stable                                                                                                                 | R      | 0              |

| 19   | CLIP<br>COS     | '1' = COS Clipping Clipping is position dependent While this bit is '1', neither the Angle/Stroke, nor the Velocity value are valid.                                                                                                                                                                                                                |        | 0              |

| 18   | CLIP<br>SIN     | '1' = SIN Clipping Clipping is position dependent While this bit is '1', neither the Angle/Stroke, nor the Velocity value are valid.                                                                                                                                                                                                                | R      | 0              |

| 17   | LOS             | '1' = SIN/COS Loss-of-Signal This bit is set when the sum of the SIN and COS signal is below 1/16 of the selected input range. I.e. with the 7,07 $V_{RMS}$ input range selected this bit is set when the sum is below 0,44 V. This bit does not necessarily invalidate the Angle/Stroke or Velocity, but signals that performance may be degraded. | R      | 0              |

| 16   | QUAD            | '1' = Quadrant-Detection Error Possible causes are: - 180° jump - Excessive rotation speed - Excessive offsets - Excessive phase shifts (> 45°) While this bit is '1', neither the Angle/Stroke, nor the Velocity value are valid.                                                                                                                  | R      | 0              |

| 15:0 | ANGLE<br>STROKE | RDC & Synchro: Angle as unsigned value: LSB = 360°/2 <sup>16</sup> LVDT modes: Stroke as signed value: LSB = ±100%/2 <sup>16</sup>                                                                                                                                                                                                                  | R      | 0              |

Table 5-5: Channel [x] Data Register with Status

#### 5.3.2.3 Channel [x] Data Register with Velocity

This register contains the angle or stroke value, with the velocity and the status bits that, when set, would invalidate the angle/stoke/velocity data.

| Bit   | Symbol          | Description                                                                                                                           | Access | Reset<br>Value |

|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31    | CLIP            | SIN/COS Clipping An OR of the CLIP COS & CLIP SIN status bits in the  "Channel [x] Data Register with Status"                         | R      | 0              |

| 30    | QUAD            | Quadrant-Detection Error As in "Channel [x] Data Register with Status"                                                                | R      | 0              |

| 29:16 | VEL             | Only valid for resolver Velocity Output in rps as signed value                                                                        | R      | 0              |

| 15:0  | ANGLE<br>STROKE | RDC & Synchro: Angle as unsigned value: LSB = $360^{\circ}/2^{16}$ LVDT modes: Stroke as signed value: LSB = $\pm 100^{\circ}/2^{16}$ | R      | 0              |

Table 5-6: Channel [x] Data Register with Velocity

#### 5.3.2.4 Channel [x] Data Register with Sample Index

| I | Bit   | Symbol          | Description                                                                                                                                                                                                                                                                                        | Access | Reset<br>Value |

|---|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| , | 31:16 | SAMIDX          | Sample count index, useful for time-based evaluation of data values, especially for LVDT sensors. SAMIDX is a counter that increments by 1 for each sample, and wraps around to zero after reaching the maximum value.  The sample rate is 4.88 µs (or every 19.53 µs when in low frequency mode). | R      | 0              |

|   | 15:0  | ANGLE<br>STROKE | RDC & Synchro: Angle as unsigned value: LSB = $360^{\circ}/2^{16}$ LVDT modes: Stroke as signed value: LSB = $\pm 100^{\circ}/2^{16}$                                                                                                                                                              | R      | 0              |

Table 5-7: Channel [x] Data Register with Sample Index

#### 5.3.2.5 Combined Data Register Channel 2 & 1 / 4 & 3

This register allows to read the data of two channels in a single access. This can be useful e.g. to read the angle of a multiturn resolver.

This register is available for Channel 2 & Channel 1 and for Channel 4 & Channel 3.

| Bit   | Symbol          | Description                                                                                                                           |   | Reset<br>Value |

|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|---|----------------|

| 31:16 | ANGLE<br>STROKE | RDC & Synchro: Angle as unsigned value: LSB = $360^{\circ}/2^{16}$ LVDT modes: Stroke as signed value: LSB = $\pm 100^{\circ}/2^{16}$ | R | 0              |

| 15:0  | ANGLE<br>STROKE | RDC & Synchro: Angle as unsigned value: LSB = $360^{\circ}/2^{16}$ LVDT modes: Stroke as signed value: LSB = $\pm 100^{\circ}/2^{16}$ | R | 0              |

Table 5-8: Combined Data Register Channel 2 & 1 / 4 & 3

## 5.3.2.6 Combined Status Register Channel 2 & 1 / 4 & 3

This register allows to read the status of two channels in a single access. This can be useful e.g. to read the status of a multiturn resolver.

This register is available for Channel 2 & Channel 1 and for Channel 4 & Channel 3.

| Bit   | Bit Symbol Description |                                                                                           | Access | Reset<br>Value |

|-------|------------------------|-------------------------------------------------------------------------------------------|--------|----------------|

| 31:16 | STATUS                 | This is a mirror of the bits [31:16] of the "Output Register with Status" for Channel 2/4 | R      | 0              |

| 15:0  | STATUS                 | This is a mirror of the bits [31:16] of the "Output Register with Status" for Channel 1/3 | R      | 0              |

Table 5-9: Combined Status Register Channel 2 & 1 / 4 & 3

### 5.3.2.7 AFE Control Register

Analog Front End (AFE) Control Register.

| Bit  | Symbol              | Description                                                                                                                                                                                                                             | Access | Reset<br>Value |

|------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:3 | -                   | Reserved                                                                                                                                                                                                                                | -      | 0              |

| 2    | AFE<br>SET<br>RANGE | Command: Set AFE Inputs Ranges Write '1' to transfer the "Input Range Register" to the AFE. Conversions will continue, observe "AFE BUSY" in the "AFE Status Register" for completion of this command. Self-clearing bit, reads as '0'. | R/W    | 0              |

| 1    | -                   | Reserved                                                                                                                                                                                                                                | -      | 0              |

| 0    | AFE<br>RESET        | Software Reset Write '1' to reset the AFE. This is a full reset to power-up default settings, including the AFE INIT. The reset status can be observed in the "AFE Status Register". Self-clearing bit, reads as '0'.                   | R/W    | 0              |

Table 5-10: AFE Control Register

## 5.3.2.8 AFE Status Register

| Bit  | Symbol      | Description                                                                                                                                                                                                                                                                                                                                                                 | Access | Reset<br>Value |

|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:8 | -           | Reserved                                                                                                                                                                                                                                                                                                                                                                    | -      | 0              |

| 2    | AFE<br>INIT | At startup the AFE initializes itself from a PROM.  '1' = Initialization done, AFE is operational  '0' = Initialization pending                                                                                                                                                                                                                                             | R      | 0              |

| 1    | AFE<br>BUSY | AFE Access is in progress. At startup this bit indicates a running AFE initialization. After startup this bit indicates running "AFE Control Register" commands. Conversions are not interrupted, but allow this bit to return to '0' before issuing a new "AFE Control Register" command.  '1' = AFE Initialization or AFE Access is in progress '0' = Idle, or converting | R      | 0              |

| 0    | AFE<br>DONE | Reset Done An AFE Reset is issued after startup, or through the AFE RESET bit in the "AFE Control Register".  '1' = Reset Done '0' = Device Reset pending                                                                                                                                                                                                                   | R      | 0              |

Table 5-11: AFE Status Register

#### 5.3.2.9 Input Range Register

Use the values in this table for the Input Range setting:

| Input Range [V <sub>RMS</sub> ]         | Setting   |

|-----------------------------------------|-----------|

| 14.14 V <sub>RMS</sub>                  | 1011      |

| 8.84 V <sub>RMS</sub>                   | 1010      |

| 7.07 V <sub>RMS</sub>                   | 1001      |

| 3.54 V <sub>RMS</sub>                   | 1000      |

| 28 V <sub>RMS</sub>                     | 0011      |

| (for TPMC151-20R Synchro-Channels only) |           |

| 14 V <sub>RMS</sub>                     | 0001      |

| (for TPMC151-20R Synchro-Channels only) |           |

| Reserved                                | All other |

Table 5-12: Input Ranges

The Input Ranges in the table are the maximum voltages for a given Input Range. The sensor voltage should be lower than that, to avoid clipping. Also refer to chapter "6. Functional Description" for further details how to setup the input range.

Use the "AFE SET RANGE" command in the "AFE Control Register" to make changes to this register active.

Changing the input range may result in step changes in the angle or stroke output data. Allow these changes to settle and check the status bits before using the angle or stroke output data.

The "RANGE SINx" and "RANGE COSx" setting of a channel must be set to the same Input Range. Synchro-Channels also use the SIN/COS range settings.

| Bit   | Symbol        | Description                        | Access | Reset<br>Value |

|-------|---------------|------------------------------------|--------|----------------|

| 31:28 | RANGE<br>COS4 | Input Range for Channel 4 COS / Lb | R/W    | 1011           |

| 27:24 | RANGE<br>SIN4 | Input Range for Channel 4 SIN / La | R/W    | 1011           |

| 23:20 | RANGE<br>COS3 | Input Range for Channel 3 COS / Lb | R/W    | 1011           |

| 19:16 | RANGE<br>SIN3 | Input Range for Channel 3 SIN / La | R/W    | 1011           |

| 15:12 | RANGE<br>COS2 | Input Range for Channel 2 COS / Lb | R/W    | 1011           |

| 11:8  | RANGE<br>SIN2 | Input Range for Channel 2 SIN / La | R/W    | 1011           |

| 7:4   | RANGE<br>COS1 | Input Range for Channel 1 COS / Lb | R/W    | 1011           |

| 3:0   | RANGE<br>SIN1 | Input Range for Channel 1 SIN / La | R/W    | 1011           |

Table 5-13: Input Range Register

#### 5.3.2.10 Channel [x] Ring Buffer Control Register

To support the measurement of singular events, the TPMC151 provides a triggerable "Ring Buffer" for each channel. When enabled, crossing a programmable trigger value starts the recording of data values, including a programmable number of pretrigger values. After finishing the recording, the Ring Buffer can be read out. The Ring Buffer length is 4096 data samples, so read the "Channel [x] Ring Buffer Data Register" 4096 times, or as long as BUF AVAIL status bit is set.

A new sample is available every  $4.88 \mu s$  (or every  $19.53 \mu s$  when in low frequency mode). To increase the record length to a certain amount, a Data Divider is provided.

Disabling the Ring Buffer resets the internal pointers, but does not clear the Buffer itself. When the Ring Buffer is enabled, but BUF AVAIL is still '0', it is possible to read old data. When reading data while BUF AVAIL is '0', the data should be treated as stale.

| Bit   | Symbol      | Description                                   |                                            |                       |       | Access | Reset<br>Value |

|-------|-------------|-----------------------------------------------|--------------------------------------------|-----------------------|-------|--------|----------------|

| 31:16 | BUF         | Ring Buffer T                                 | R/W                                        | 0000                  |       |        |                |

|       | TRIG        | _                                             | Trigger Level starts t                     | he recording          |       |        |                |

| 15:4  | PRE<br>TRIG |                                               | ta values stored beforesulting number of I |                       |       | R/W    | 0000           |

| 3:2   | BUF<br>DIV  | Ring Buffer D<br>To increase to<br>be stored: | ata Divider<br>ne recording time, on       | ly the nth data value | e can | R/W    | 00             |

|       |             | Div                                           | Store                                      | Recording Time        |       |        |                |

|       |             | 00                                            | every value                                | 20 ms                 |       |        |                |

|       |             | 01                                            | every 2nd value                            | 40 ms                 |       |        |                |

|       |             | 10                                            | every 4th value                            | 80 ms                 |       |        |                |

|       |             | 11                                            | every 8th value                            | 160 ms                |       |        |                |

|       |             | When in low to quadrupled.                    | requency mode, the                         | Recording Time is     |       |        |                |

| 1:0   |             |                                               |                                            |                       | tions | R/W    | 00             |

|       |             | Edge                                          | Description                                |                       |       |        |                |

|       |             | 00                                            | Ring Buffer disab                          | led                   |       |        |                |

|       |             | 01                                            | Trigger by low-to-                         | high transitions      |       |        |                |

|       |             | 10                                            | Trigger by high-to                         | o-low transitions     |       |        |                |

|       |             | 11                                            | Both                                       |                       | 1     |        |                |

|       |             |                                               |                                            |                       | _     |        |                |

Table 5-14: Channel [x] Ring Buffer Control Register

### 5.3.2.11 Channel [x] Ring Buffer Status Register

| Bit  | Symbol       | Description                                                                                | Access | Reset<br>Value |

|------|--------------|--------------------------------------------------------------------------------------------|--------|----------------|

| 31:2 | -            | Reserved                                                                                   | -      | -              |

| 1    | BUF<br>AVAIL | '1' = Data is available. Set when the recording has finished, reset when all data was read | R      | 0              |

| 0    | BUF<br>TRGD  | '1' = Trigger event occurred, the Ring Buffer is filling with post trigger samples         | R      | 0              |

Table 5-15: Channel [x] Ring Buffer Status Register

### 5.3.2.12 Channel [x] Ring Buffer Data Register

The Ring Buffer contains the angle or stroke value, the velocity and the status bits that, when set, would invalidate the angle/stoke/velocity data. This is equivalent to the "Channel [x] Data Register with Velocity".

| Bit   | Symbol          | Description                                                                                                   | Access | Reset<br>Value |

|-------|-----------------|---------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31    | CLIP            | SIN/COS Clipping An OR of the CLIP COS & CLIP SIN status bits in the  "Channel [x] Data Register with Status" | R      | 0              |

| 30    | QUAD            | Quadrant-Detection Error As in "Channel [x] Data Register with Status"                                        | R      | 0              |

| 29:16 | VEL             | Velocity As in "Channel [x] Data Register with Velocity"                                                      | R      | 0              |

| 15:0  | ANGLE<br>STROKE | Resolver angle / LVDT stroke As in "Channel [x] Data Register"                                                | R      | 0              |

Table 5-16: Channel [x] Ring Buffer Data Register

#### 5.3.2.13 Global Registers

#### 5.3.2.13.1 Global Control Register

The channel mode is not only the selection of the sensor type.

"RDC" and "Synchro" work basically the same, except for how the low frequency mode works. When the input excitation frequency is lower than 4 kHz, the TPMC151 enters a low frequency mode. This is indicated by the "LOF" status bit.

The low frequency mode adapts internal filter times to the lower excitation frequency. In consequence, the reaction to angle and stroke changes is slower, and settling out step changes takes more time. In the "Synchro" mode, this time is increased to allow the use of excitation frequencies down to 400 Hz.

All modes behave the same for input excitation frequencies above 4 kHz. Only the "Synchro" shows the increased internal filter times in the low frequency mode.

| Bit  | Symbol | Descrip | ption     |                              | Access | Reset<br>Value |

|------|--------|---------|-----------|------------------------------|--------|----------------|

| 31:1 | -      | Reserve | ed        |                              | -      | -              |

| 7:6  | MODE4  | Mode C  | Channel - | 4                            | R/W    | 00             |

|      |        | Same a  | as below  |                              |        |                |

| 5:4  | MODE3  | Mode C  | Channel   | 3                            | R/W    | 00             |

|      |        | Same a  | as below  |                              |        |                |

| 3:2  | MODE2  | Mode C  | Channel   | R/W                          | 00     |                |

|      |        | Same a  | as below  |                              |        |                |

| 1:0  | MODE1  | Mode C  | Channel   | 1                            | R/W    | 00             |

|      |        |         | Mode      | Description                  |        |                |

|      |        |         | 00        | RDC                          |        |                |

|      |        |         | 01        | Synchro                      |        |                |

|      |        |         | 10        | Differential LVDT (A / B)    |        |                |

|      |        |         | 11        | Ratiometric LVDT (A-B / A+B) |        |                |

|      |        |         |           |                              |        |                |

Table 5-17: Global Control Register

#### 5.3.2.13.2 Status Register

This register provides a summary of the status bits in "Channel [x] Data Register with Status" from all four channels. It also latches the volatile status bits, allowing to catch intermediate error states. Latched bits are marked with a "R/C" access and must be reset by writing a '1' to the bit. The latched status bits in this register are used for interrupt generation. Latching is only done when the channel's INIT DONE bit is set, so that error states during the initialization are inhibited, with the AMP OT bits as exception: An interrupt will be generated when the EXC ENA bit is reset due to an overtemperature condition signaled by the excitation amplifier.

Status bits that are set back to '1' immediately after a clear, indicate persisting status conditions.

Static status bits are marked with a "R" access and do not need to be reset.

| Bit   | Symbol                | Description                                                                                                                                                                                                                                                                                                                                                  | Access | Reset<br>Value |

|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:28 | -                     | Status for Channel 4                                                                                                                                                                                                                                                                                                                                         | -      | 0              |

| 23:16 | -                     | Status for Channel 3                                                                                                                                                                                                                                                                                                                                         | -      | 0              |

| 15:8  | -                     | Status for Channel 2                                                                                                                                                                                                                                                                                                                                         | -      | 0              |

| 7     | INIT<br>DONE<br>(CH1) | '1' = RDC initialization done & output is valid                                                                                                                                                                                                                                                                                                              | R      | 0              |

| 6     | LOF<br>(CH1)          | '1' = RDC entered low frequency mode This bit is set when the Excitation frequency is lower than 4 kHz                                                                                                                                                                                                                                                       | R      | 0              |

| 5     | EXC<br>HIGH<br>(CH1)  | '1' = Excitation Frequency too high,<br>f <sub>EXC</sub> > 20 kHz                                                                                                                                                                                                                                                                                            | R      | 0              |

| 4     | EXC<br>LOW<br>(CH1)   | '1' = Excitation Frequency too low f <sub>EXC</sub> < 400 Hz in "Synchro"-mode f <sub>EXC</sub> < 1 kHz in all other modes.                                                                                                                                                                                                                                  | R      | 0              |

| 3     | AMP<br>OT<br>(CH1)    | '1' = Excitation Output Overtemperature Flag The excitation amplifier signaled an overtemperature condition                                                                                                                                                                                                                                                  | R/C    | 0              |

| 2     | CLIP<br>(CH1)         | '1' = A Clipping Error occurred This is an OR of the CLIP SIN and CLIP COS bits in the "Channel [x] Data Register with Status" register                                                                                                                                                                                                                      | R/C    | 0              |

| 1     | LOS<br>(CH1)          | '1' = A Loss-of-Signal Error occurred This bit is set when the sum of the SIN and COS signal is below 1/16 of the selected input range. I.e. with the 7,07 $V_{RMS}$ input range selected this bit is set when the sum is below 0,44 V. This bit does not necessarily invalidate the Angle/Stroke or Velocity, but signals that performance may be degraded. | R/C    | 0              |

| 0     | QUAD<br>(CH1)         | '1' = A Quadrant-Detection Error occurred Possible causes are: - 180° jump - Excessive rotation speed - Excessive offsets - Excessive phase shifts (> 45°)                                                                                                                                                                                                   | R/C    | 0              |

Table 5-18: Status Register

### 5.3.2.13.3 Interrupt Enable Register

For pending interrupts and interrupt acknowledge see the Interrupt Status Register.

| Bit   | Symbol          | Description                                                                                                                                                                                                            | Access | Reset<br>Value |

|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31    | IRQ ACK<br>CONF | Interrupt Acknowledge Configuration  0 = Interrupts are acknowledged by writing '1' to the appropriate bit in the "Interrupt Status Register"  1 = Interrupts are cleared when the "Interrupt Status Register" is read | R/W    | 0              |

| 30:21 | -               | Reserved, always reads as '0'                                                                                                                                                                                          | -      | 0              |

| 20    | TIEN            | Interval Timer Interrupt An interrupt is generated when the Interval Timer reaches zero                                                                                                                                | R/W    | 0              |

| 19    | BUF DONE 4      | Ring Buffer Data recording finished IRQ                                                                                                                                                                                | R/W    | 0              |

| 18    | BUF DONE 3      | 1 = Ring Buffer Data Interrupt enabled                                                                                                                                                                                 | R/W    | 0              |

| 17    | BUF DONE 2      | 0 = Ring Buffer Data Interrupt disabled                                                                                                                                                                                | R/W    | 0              |

| 16    | BUF DONE 1      | n interrupt will be generated when the recording has<br>nished                                                                                                                                                         | R/W    | 0              |

| 15    | AMP OT 4        | Excitation Amplifier Overtemperature IRQ                                                                                                                                                                               | R/W    | 0              |

| 14    | AMP OT 3        | 1 = Excitation Amplifier Overtemperature Interrupt                                                                                                                                                                     | R/W    | 0              |