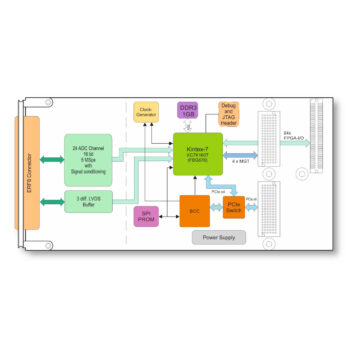

The TXMC638 is a standard single-width Switched Mezzanine Card (XMC) compatible module providing a user configurable AMD Kintex™ 7 FPGA with 24 ADC input channel.

The TXMC638 ADC input channels are based on the Linear Dual 16-Bit 5Msps Differential LTC2323-16 ADC. Each of the 24 channels has a resolution of 16bit and can work with up to 5 Msps. The analog input circuit is designed to allow input voltages up to ±2.5 V on each input-pin (results in ±5 V differential voltage range)

For customer specific I/O extension or inter-board communication, the TXMC638 provides 64 I/Os on P14 and 4 Multi-Gigabit-Transceiver on P16. The P14 I/O lines are connected directly to the FPGA and can be used as 64 single ended LVCMOS25 or as 32 differential LVDS25 interface be using I/O configuration of the FPGA.

Additionally the TXMC638 provides three 100 Ohm terminated ac-coupled, differential inputs with wide Input voltage range.

All these front I/O lines like the ADC interface and the three 100 Ohm inputs are connected to a 98-pin. Samtec ERF8-049 Rugged EdgeRate Connector.

A 1 GB, 32 bit wide DDR3 SDRAM is connected to the User FPGA. The SDRAM-Interface uses an internal Memory Controller of the Kintex 7.

The User FPGA is configured by a serial SPI flash. For full PCIe specification compliance, the XILINX Tandem Configuration Feature can be used for FPGA configuration. XILINX Tandem Methodologies Tandem PROM should be the favored Methodology. The SPI flash device is in-system programmable. An in-circuit debugging option is available via a JTAG header for read back and real-time debugging of the FPGA design (using Xilinx ChipScope).

User applications for the TXMC638 with AMD Kintex™ 7 FPGA can be can be developed using the AMD Vivado™ design tool. A license for the Vivado Design Suite design tool is required.

TEWS offers a well-documented FPGA Board Reference Design. It includes a constraint file with all necessary pin assignments and basic timing constraints. The FPGA Board Reference Design covers the main functionalities of the TXMC638.

The TXMC638 is delivered with the FPGA Board Reference Design. The user FPGA could be programmed via the on-board Board Configuration Controller (BCC). Programming via JTAG interface using an XILINX USB programmer is also possible. In accordance with the PCI specification and the buffering of PCI header data, the contents of the user FPGA can be changed during operation.