The TPMC363 is a conduction cooled single-width 32 bit PMC with four high speed serial data communication channels.

The TPMC363 is the successor of the discontinued TPMC362, providing similar functionality and full connector and pin-out compatibility.

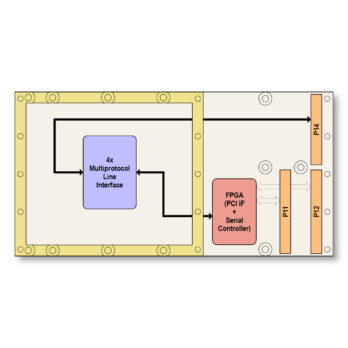

The serial communication controller is implemented in FPGA logic, along with the bus master capable PCI interface, guaranteeing long term availability and having the option to implement additional functions in the future.

Each channel provides dedicated receive and transmit FIFOs for high data throughput.

Data transfer on the PCI bus is handled via TPMC363 initiated DMA cycles with minimum host/CPU intervention.

Several serial communication protocols are supported by each channel, such as asynchronous, isochronous, synchronous and HDLC mode.

A 14.7456 MHz oscillator provides standard asynchronous baud rates. An additional 24 MHz oscillator is provided for other baud rates. A 10 MHz oscillator is used for the synchronous baud rate of 10 Mbit/s.

Each channel also provides various interrupt sources, generated on INTA. The interrupt sources can be enabled or disabled individually.

Multiprotocol transceivers are used for the line interface. The physical interface is selectable by software, individually for each channel as EIA-232, EIA-422, EIA449, EIA-530, EIA-530A, V.35, V.36 or X.21.

The following signals are provided by the TPMC363 for each channel at the front and rear-I/O connectors:

Receive Data (RxD +/-), Transmit Data (TxD +/-), Receive Clock (RxC +/-), Transmit Clock (TxC +/-), Ready-To-Send (RTS +/-), Clear-To-Send (CTS +/-), Carrier-Detect (CD +/-) and GND.

The TPMC363 provides rear panel I/O via P14.

Software Support (TDRV009-SW-xx) for different operating systems is available.