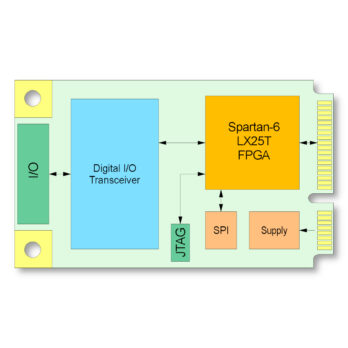

The TMPE633 is a standard full PCI Express Mini Card, providing a user programmable AMD Spartan ™ 6 LX25T FPGA.

The TMPE633-10R provides 26 ESD-protected 5V-tolerant TTL lines, the TMPE633-11R provides 13 differential I/O lines using EIA 422 / EIA 485 compatible, ESD-protected line transceivers and the TMPE633-12R provides 13 differential I/O lines using Multipoint-LVDS Transceiver.

All I/O lines are individually programmable as input or output. TTL I/O lines can be set to high, low, or tristate. Each TTL I/O line has a pull-resistor to a common programmable pull voltage that can be set so +3.3 V, +5 V and GND. Differential I/O lines are terminated, RS-485 lines with 120 ohms, M-LVDS lines with 100 ohms.

The I/O signals are accessible through a 30 pin Pico-Clasp latching connector.

The User FPGA is configured by a SPI flash. An in-circuit debugging option is available via a JTAG header for read back and real-time debugging of the FPGA design (using AMD ChipScope ™). For direct JTAG access to the FPGA using the Xilinx Platform Cable USB, the TA308 Programming Kit is required.

User applications for the TMPE633 with AMD Spartan ™ 6 FPGA (XC6SLX25T-2) can be developed using the design software AMD ISE ™ WebPACK, which can be downloaded free of charge from www.amd.com.

TEWS offers a well-documented basic FPGA Example Application design. It includes an .ucf file with all necessary pin assignments and basic timing constraints. The example design covers the main functionalities of the TMPE633. It implements local Bus interface to local Bridge device, register mapping and basic I/O. It comes as am AMD ISE ™ project with source code and as a ready-to-download bit stream.

Please note: The basic example design requires the Embedded Development Kit (EDK), which is part of the Embedded or System Edition of the ISE ™ Design Suite from AMD (downloadable from www.amd.com, a 30 day evaluation license is available).